Use FPGA como atalho mais rápido para elaborar aplicações de ponta em IA de alto desempenho e de eficiência energética

Contributed By DigiKey's North American Editors

2021-01-12

Os projetistas que buscam implementar algoritmos de inteligência artificial (IA) nos processadores de inferência na borda, estão sob pressão constante para reduzir o consumo de energia e o tempo de desenvolvimento, mesmo com o aumento das demandas de processamento. As matrizes de porta programável no campo (FPGAs) oferecem uma combinação especialmente efetiva de velocidade e eficiência de energia para implementação de mecanismos de inferência de rede neural (NN) necessários para IA na borda. Contudo, para desenvolvedores não familiarizados com FPGAs, os métodos de desenvolvimento convencional de FPGA podem parecer complexos, muitas vezes levando os desenvolvedores a optarem por soluções menos indicadas.

Este artigo descreve uma abordagem mais simples da Microchip Technology que permite aos desenvolvedores contornar o desenvolvimento tradicional do FPGA para criar NNs treinadas usando FPGAs e um kit de desenvolvimento de software (SDK), ou usar um kit de vídeo baseado em FPGA para passar imediatamente para o desenvolvimento de aplicação de visão embarcada inteligente.

Por que usar IA na borda?

A computação de borda, ou edge computing, trás uma série de benefícios às aplicações de Internet das Coisas (IoT) em setores tão variados quanto automação industrial, sistemas de segurança, casas inteligentes, entre outros. Numa aplicação industrial de IoT (IIoT) destinada ao chão de fábrica, edge computing pode melhorar drasticamente o tempo de resposta em ciclos do controle de processo ao eliminar atrasos de idas e vindas das aplicações baseadas em nuvem. De forma semelhante, um sistema de segurança baseado em borda, ou fechadura da porta de casa inteligente, pode continuar a funcionar mesmo quando a conexão à nuvem for perdida de forma acidental ou intencional. Em muitos casos, o uso de edge computing em quaisquer dessas aplicações pode ajudar a reduzir o custo geral de operação, através da redução da dependência do produto nos recursos da nuvem. Em vez de enfrentar uma necessidade não prevista para recursos adicionais e caros da nuvem, conforme aumenta a demanda dos produtos, os desenvolvedores podem contar com recursos de processamento local, integrados em seus produtos para ajudar a manter as despesas operacionais mais estáveis.

A aceitação rápida e maior demanda por modelos de inferência de aprendizado de máquina (ML) aumenta drasticamente a importância de edge computing. Para os desenvolvedores, o processamento local dos modelos de inferência ajuda a reduzir a latência de resposta e os custos dos recursos da nuvem para inferência baseada em nuvem. Para os usuários, o uso de modelos locais de inferência acrescenta a confiança de que os produtos continuarão a funcionar, apesar da perda ocasional de conectividade com a Internet ou alterações nas ofertas baseadas em nuvem do fornecedor do produto. Além disso, as preocupações sobre segurança e privacidade podem impulsionar ainda mais a necessidade de processamento local e inferência para limitar a quantidade de informações confidenciais que são transferidas à nuvem pela internet pública.

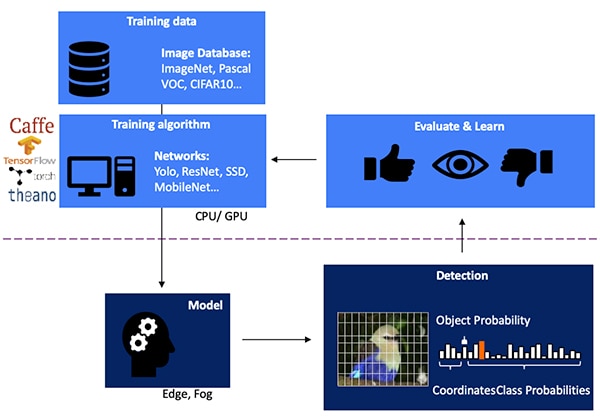

Desenvolver um modelo de inferência NN para detecção de objeto baseado em visão é um processo de várias etapas, começando com treinamento do modelo, normalmente desempenhado sobre estrutura de ML, como TensorFlow, usando imagens rotuladas de publicidade disponível ou personalizadas. Por causa das demandas de processamento, o treinamento do modelo é normalmente realizado com unidades de processamento gráfico (GPUs) na nuvem ou em outra plataforma de computação de alto desempenho. Após feito o treinamento, o modelo é convertido a um modelo de inferência capaz de executar recursos em edge computing ou fog computing e fornecer os resultados de inferência como um conjunto de probabilidades de classe de objeto (figura 1).

Figura 1: a implementação de um modelo de inferência para o IA de borda encontra-se no final de um processo de várias etapas que exige treinamento e otimização de NNs em estruturas usando dados de treinamento disponíveis ou personalizados. (Fonte da imagem: Microchip Technology)

Figura 1: a implementação de um modelo de inferência para o IA de borda encontra-se no final de um processo de várias etapas que exige treinamento e otimização de NNs em estruturas usando dados de treinamento disponíveis ou personalizados. (Fonte da imagem: Microchip Technology)

Por que os modelos de inferência são um desafio computacional

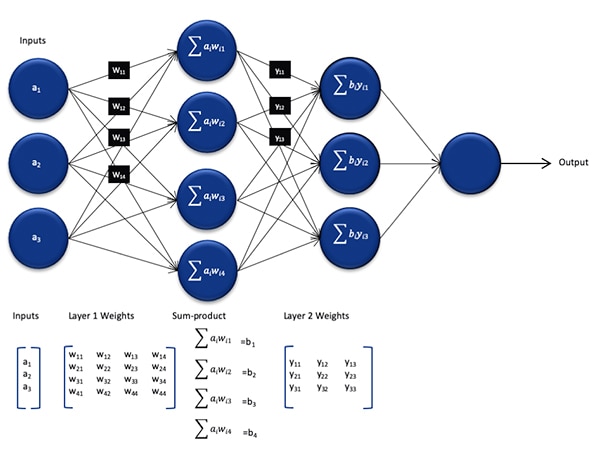

Embora sejam menores em tamanho e complexidade quando comparados aos modelos usados durante o processo de treinamento, um modelo de inferência NN ainda apresenta um desafio computacional para os processadores de uso geral devido ao número grande de cálculos que ele exige. Na sua forma genérica, um modelo NN profundo compreende várias camadas de conjuntos de neurônios. Dentro de cada camada numa rede conectada, cada neurônio nij precisa computar a soma dos produtos de cada entrada com um peso associado wij (figura 2).

Figura 2: a quantidade de cálculos necessários para inferência com uma NN pode impor uma sobrecarga computacional significativa. (Fonte da imagem: Microchip Technology)

Figura 2: a quantidade de cálculos necessários para inferência com uma NN pode impor uma sobrecarga computacional significativa. (Fonte da imagem: Microchip Technology)

Não é mostrado na figura 2 o requisito computacional adicional imposto pela função de ativação que modifica a saída de cada neurônio através do mapeamento dos valores negativos até o zero, valores de mapeamento maiores que 1 para 1 e funções semelhantes. A saída da função de ativação para cada neurônio nij serve como a entrada para a próxima camada i+1, continuando desta forma para cada camada. Finalmente, a camada de saída do modelo NN produz um vetor de saída que representa a probabilidade de que o vetor de entrada original (ou matriz) corresponda a uma das classes (ou rótulos) usadas durante o processo de aprendizado supervisionado.

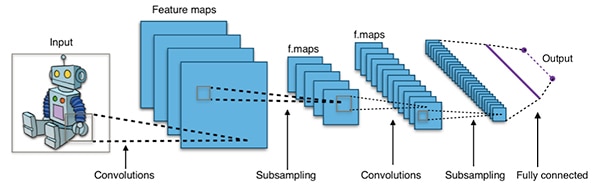

Na prática, os modelos NN são embutidos em arquiteturas muito maiores e mais complexas do que a arquitetura NN genérica representada acima. Por exemplo, uma NN convolucional (CNN) típica usada para detecção de objeto de imagem aplica esses princípios de forma fragmentada, varrendo a largura, altura e profundidade de cor de uma imagem de entrada para produzir uma série de mapas de características que, por fim, rende o vetor de predição de saída (figura 3).

Figura 3: as CNNs usadas para detecção de objeto de imagem envolvem grande quantidade de neurônios em muitas camadas, exigindo maior demanda na plataforma de computação. (Fonte da imagem: Aphex34 CC BY-SA 4.0)

Figura 3: as CNNs usadas para detecção de objeto de imagem envolvem grande quantidade de neurônios em muitas camadas, exigindo maior demanda na plataforma de computação. (Fonte da imagem: Aphex34 CC BY-SA 4.0)

Usando FPGAs para acelerar a matemática da NN

Embora uma série de opções continuem a surgir para executar modelos de inferência na borda, algumas alternativas fornecem uma combinação ótima de flexibilidade, desempenho e eficiência de energia necessária para inferência prática de alta velocidade na borda. Entre as alternativas prontamente disponíveis para IA na borda, os FPGAs são especialmente eficazes porque podem fornecer execução de operações intensas de computação baseadas em hardware e de alto desempenho, aliado ao consumo de energia relativamente baixo.

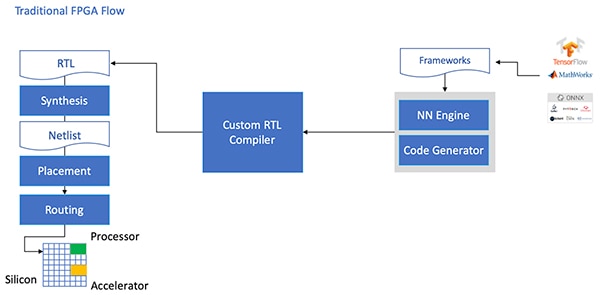

Apesar das vantagens, algumas vezes, os FPGAs são esquecidos devido ao fluxo de desenvolvimento tradicional que pode ser assustador aos desenvolvedores sem muita experiência em FPGA. Para criar uma implementação prática de FPGA de um modelo NN gerado por uma estrutura NN, o desenvolvedor precisaria compreender as nuanças de conversão do modelo para a linguagem de transferência do registros (RTL), sintetizando o projeto, e trabalhando com o local final e o estágio do projeto físico da rota para produzir uma implementação otimizada (figura 4).

Figura 4: para implementar um modelo NN em um FPGA, os desenvolvedores precisavam, até agora, compreender como converter seus modelos para RTL e trabalhar através do fluxo tradicional de FPGA. (Fonte da imagem: Microchip Technology)

Figura 4: para implementar um modelo NN em um FPGA, os desenvolvedores precisavam, até agora, compreender como converter seus modelos para RTL e trabalhar através do fluxo tradicional de FPGA. (Fonte da imagem: Microchip Technology)

Com os FPGAs PolarFire, software especializado e propriedade intelectual associada (IP), a Microchip Technology fornece uma solução que torna a inferência na borda, de baixo consumo e alto desempenho, amplamente disponível aos desenvolvedores sem experiência em FPGA.

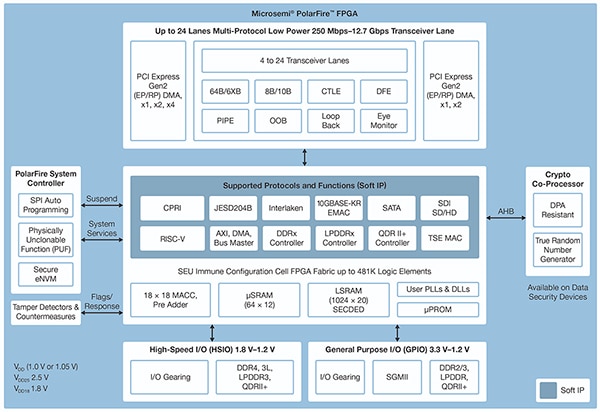

Fabricados numa tecnologia avançada de processo não volátil, os FPGAs PolarFire foram projetados para maximizar a flexibilidade e o desempenho, além de minimizar o consumo de energia. Junto com uma extensa matriz de interfaces de alta velocidade para comunicações e entrada/saída (E/S), eles apresentam um tecido profundo de FPGA capaz de suportar funcionalidades avançadas usando núcleos IP brandos, incluindo processadores RISC-V, controladores avançados de memória e outros subsistemas de interface padrão (figura 5).

Figura 5: a arquitetura PolarFire da Microchip Technology fornece um tecido profundo projetado para suportar requisitos de projeto de alto desempenho, incluindo implementação de modelos de inferência de computação intensiva. (Fonte da imagem: Microchip Technology)

Figura 5: a arquitetura PolarFire da Microchip Technology fornece um tecido profundo projetado para suportar requisitos de projeto de alto desempenho, incluindo implementação de modelos de inferência de computação intensiva. (Fonte da imagem: Microchip Technology)

O tecido FPGA PolarFire fornece um extenso conjunto de elementos lógicos e blocos específicos, com suporte em uma variedade de capacidades de membros diferentes da família FPGA PolarFire, incluindo as séries MPF100T, MPF200T, MPF300T e MPF500T (tabela 1).

|

Tabela 1: uma variedade de recursos e capacidades do tecido FPGA está disponível na série PolarFire. (Fonte da imagem: DigiKey, baseada na ficha técnica PolarFire da Microchip Technology)

Entre os recursos de interesse específico para aceleração de inferência, a arquitetura PolarFire inclui um bloco matemático dedicado que fornece uma função multiplicar-acumular (MAC) assinada de 18 x 18 bits com um pré-somador. Um modo integrado do produto de pontos usa um único bloco matemático para realizar duas operações de multiplicação de 8 bits, fornecendo um mecanismo para aumentar a capacidade tirando vantagem do impacto negligenciável da quantização do modelo na precisão.

Além de acelerar as operações matemáticas, a arquitetura PolarFire ajuda a aliviar o tipo de congestionamento de memória encontrado ao implementar modelos de inferência nas arquiteturas de uso geral, como pequenas memórias distribuídas para armazenar resultados intermediários, criadas durante a execução do algoritmo NN. Da mesma forma, pesos e valores de polarização do modelo NN podem ser armazenados numa memória de somente leitura (ROM) de profundidade 16 e coeficiente de 18 bits, construída a partir de elementos lógicos localizados próximos ao bloco matemático.

Combinado com outros recursos do tecido FPGA PolarFire, os blocos matemáticos fornecem a base para o CoreVectorBlox IP de nível mais alto da Microchip Technology. Isso serve com um mecanismo NN flexível capaz de executar tipos diferentes de NNs. Junto com um conjunto de registradores de controle, o CoreVectorBlox IP inclui três blocos maiores funcionais:

- Microcontrolador: um simples processador de software RISC-V que lê o objeto binário grande (BLOB) de firmware da Microchip e o arquivo NN BLOB específico do usuário a partir do armazenamento externo. Ele controla as operações gerais do CoreVectorBlox executando instruções a partir do BLOB de firmware.

- Processador de matriz (MXP): um processador de software que compreende oito unidades lógicas e aritméticas (ALUs) de 32 bits, projetado para realizar operações paralelas nos vetores de dados usando operações de tensor element-wise, incluindo add, sub, xor, shift, mul, dotprod e outras, através de precisão mista de 8, 16 e 32 bits, conforme for necessário.

- Acelerador CNN: acelera as operações MXP usando uma matriz bidimensional das funções MAC implementadas através de blocos matemáticos e operação com precisão de 8 bits.

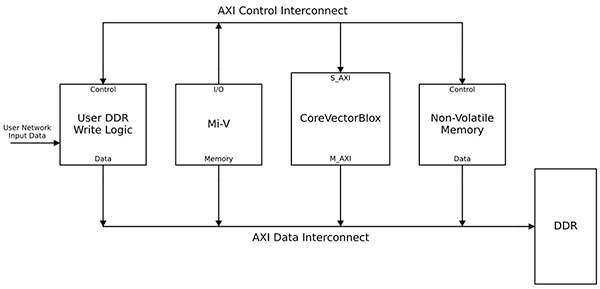

Um sistema completo de processamento NN combinaria um bloco CoreVectorBlox IP, memória, controlador de memória e um processador hospedeiro, como o núcleo do processador de software Microsoft RISC-V (Mi-V) (figura 6).

Figura 6: o bloco IP CoreVectorBlox trabalha com um processador hospedeiro, como o microcontrolador Mi-V RISC-V da Microchip, para implementar um modelo de inferência NN. (Fonte da imagem: Microchip Technology)

Figura 6: o bloco IP CoreVectorBlox trabalha com um processador hospedeiro, como o microcontrolador Mi-V RISC-V da Microchip, para implementar um modelo de inferência NN. (Fonte da imagem: Microchip Technology)

Numa implementação de sistema de vídeo, o processador hospedeiro carregaria o firmware e BLOBs de rede a partir do sistema de memória flash e os copiaria dentro da memória de acesso aleatório (RAM) de taxa de dados dupla (DDR), para uso do bloco CoreVectorBlox. Conforme os quadros de vídeo chegam, o processador hospedeiro os escreve dentro da RAM DDR e sinaliza o bloco CoreVectorBlox para começar o processamento da imagem. Após executar o modelo de inferência definido no BLOB de rede, o bloco CoreVectorBlox escreve os resultados, incluindo classificação de imagem, de volta a RAM DDR para uso pela aplicação de destino.

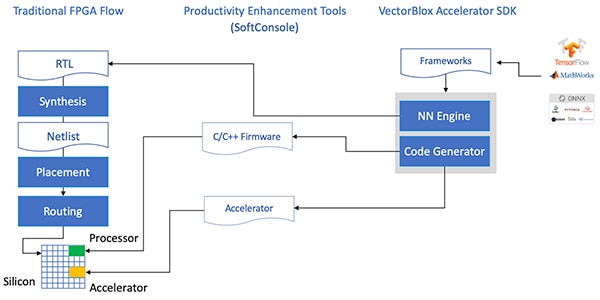

O fluxo de desenvolvimento simplifica a implementação FPGA NN

A Microchip protege os desenvolvedores da complexidade de implementação de um modelo de inferência NN nos FPGAs PolarFire. Em vez de lidar com os detalhes do fluxo FPGA tradicional, os desenvolvedores de modelo NN trabalham com suas estruturas NN de forma usual, e carregam o modelo resultante no Kit de Desenvolvimento de Software VectorBlox Accelerator (SDK) da Microchip Technology. O SDK gera o conjunto de arquivos necessários, incluindo aqueles para o fluxo de desenvolvimento FPGA normal, o firmware e os arquivos BLOB de rede, citados anteriormente (figura 7).

Figura 7: o SDK VectorBlox Accelerator gerencia os detalhes de implementação de um modelo NN em um FPGA, gerando automaticamente os arquivos necessários para projetar e executar o modelo de inferência baseado em FPGA. (Fonte da imagem: Microchip Technology)

Figura 7: o SDK VectorBlox Accelerator gerencia os detalhes de implementação de um modelo NN em um FPGA, gerando automaticamente os arquivos necessários para projetar e executar o modelo de inferência baseado em FPGA. (Fonte da imagem: Microchip Technology)

Devido o fluxo do SDK VectorBlox Accelerator sobrepor o projeto NN sobre o mecanismo NN implementado no FPGA, as NNs diferentes podem ser executadas no mesmo projeto FPGA sem a necessidade de refazer o fluxo de síntese do projeto FPGA. Os desenvolvedores criam um código C/C++ para o sistema resultante e são capazes de alternar modelos dentro do sistema em tempo real ou executar modelos simultaneamente usando divisão de tempo.

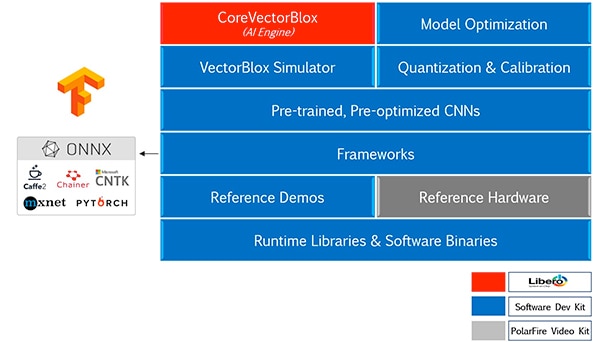

O SDK VectorBlox Accelerator combina a suíte de projeto FPGA Libero da Microchip Technology com um conjunto abrangente de recursos para o desenvolvimento de modelos de inferência NN. Junto com a otimização de modelo, quantização e serviços de calibração, o SDK fornece um simulador NN que permite aos desenvolvedores usar os mesmos arquivos BLOB para avaliar seu modelo antes de usá-lo na implementação de hardware FPGA (figura 8).

Figura 8: o SDK VectorBlox Accelerator fornece um conjunto abrangente de serviços projetados para otimizar a implementação FPGA de modelos de inferência gerados por estrutura. (Fonte da imagem: Microchip Technology)

Figura 8: o SDK VectorBlox Accelerator fornece um conjunto abrangente de serviços projetados para otimizar a implementação FPGA de modelos de inferência gerados por estrutura. (Fonte da imagem: Microchip Technology)

O SDK VectorBlox Accelerator suporta modelos no formato Open Neural Network Exchange (ONNX), bem como modelos de uma série de estruturas, incluindo TensorFlow, Caffe, Chainer, PyTorch e MXNET. As arquiteturas CNN com suporte incluem MNIST, versões da MobileNet, ResNet-50, Tiny Yolo V2 e Tiny Yolo V3. A Microchip está trabalhando para expandir esse suporte e incluir muitas redes no zoo de modelo aberto do toolkit OpenVINO de código aberto dos modelos pré-treinados, incluindo Yolo V3, Yolo V4, RetinaNet, SSD-MobileNet, entre muitos outros.

O kit de vídeo demonstra a inferência FPGA

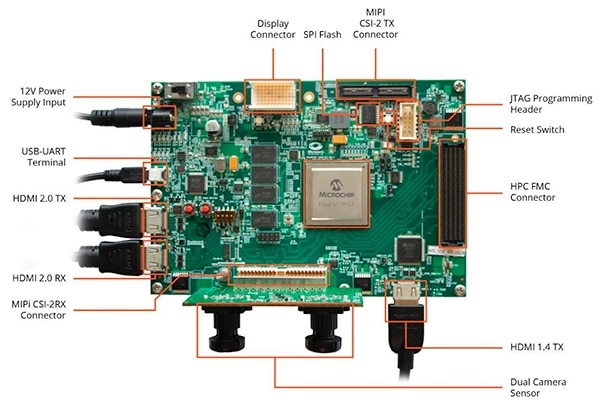

Para ajudar os desenvolvedores a passar rapidamente ao desenvolvimento de aplicação de visão inteligente embarcada, a Microchip Technology fornece uma aplicação abrangente de amostra projetada para executar no kit de imagem e vídeo FPGA MPF300-VIDEO-KIT e projeto de referência da empresa.

Baseado no FPGA MPF300T PolarFire da Microchip, a placa do kit combina dois sensores de câmera, RAM de taxa de dados dupla 4 (DDR4), memória flash, gerenciamento de energia e uma variedade de interfaces (figura 9).

Figura 9: o kit de vídeo e imagem FPGA PolarFire MPF300-VIDEO-KIT e software associado fornecem aos desenvolvedores um início rápido à inferência baseada em FPGA em aplicações de visão inteligente embarcada. (Fonte da imagem: Microchip Technology)

Figura 9: o kit de vídeo e imagem FPGA PolarFire MPF300-VIDEO-KIT e software associado fornecem aos desenvolvedores um início rápido à inferência baseada em FPGA em aplicações de visão inteligente embarcada. (Fonte da imagem: Microchip Technology)

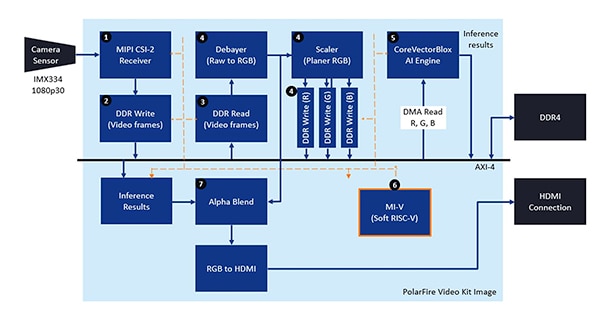

O kit vem com um projeto de design Libero completo usado para gerar o firmware e arquivos BLOB de rede. Após programar os arquivos BLOB na memória flash da placa, os desenvolvedores clicam no botão de execução no Libero para iniciar a demonstração, que processa as imagens de vídeo a partir do sensor da câmera e exibe os resultados de inferência em um display (figura 10).

Figura 10: o kit de vídeo e imagem FPGA PolarFire da Microchip Technology demonstra como projetar e usar uma implementação FPGA de um sistema de visão inteligente embarcado, construído com base no mecanismo NN CoreVectorBlox. (Fonte da imagem: Microchip Technology)

Figura 10: o kit de vídeo e imagem FPGA PolarFire da Microchip Technology demonstra como projetar e usar uma implementação FPGA de um sistema de visão inteligente embarcado, construído com base no mecanismo NN CoreVectorBlox. (Fonte da imagem: Microchip Technology)

Para cada quadro de vídeo de entrada, o sistema baseado em FPGA executa as seguintes etapas (com correlação dos números das etapas à figura 10):

- Carrega um quadro a partir da câmera

- Armazena o quadro na RAM

- Lê o quadro a partir da RAM

- Converte a imagem bruta para RGB, suaviza o RGB e armazena o resultado na RAM

- O processador de software RISC-V Mi-V inicia o mecanismo CoreVectorBlox, que recupera a imagem a partir da RAM, realiza a inferência e armazena os resultados da probabilidade de classificação de volta para a RAM

- O Mi-V usa os resultados para criar um quadro sobreposto com as caixas delimitadoras, resultados de classificação e outros metadados e armazena o quadro na RAM

- O quadro original é mesclado com o quadro sobreposto e escrito no display HDMI

A demonstração aceita suporte de aceleração dos modelos Tiny Yolo V3 e MobileNet V2, mas os desenvolvedores podem executar outros modelos com suporte SDK usando os métodos descritos previamente, fazendo uma pequena alteração de código para acrescentar o nome do modelo e metadados à lista existente contendo os dois modelos padrões.

Conclusão

Normalmente, os algoritmos de IA como os modelos NN impõem cargas de trabalho de computação intensiva, que requer mais recursos robustos de computação do que aqueles disponíveis pelos processadores de uso geral. Embora os FPGAs estejam bem equipados para atender as exigências de desempenho e baixo consumo na execução dos modelos de inferência, os métodos convencionais de desenvolvimento FPGA podem ser complexos, muitas vezes levando os desenvolvedores a optarem por soluções menos indicadas.

Conforme mostrado, ao usar software e IP específico da Microchip Technology, os desenvolvedores sem experiência em FPGA podem implementar projetos baseados em inferência capazes de atender melhor o desempenho e consumo, assim como as exigências de cronograma do projeto.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.