Como implementar a contenção de repique via hardware para interruptores e relés quando a opção via software não é adequada

Contributed By DigiKey's North American Editors

2021-02-09

No contexto da engenharia elétrica e eletrônica, uma chave é um componente que pode "fechar" ou "abrir" um circuito elétrico, interrompendo assim uma corrente elétrica ou desviando-a de um condutor para outro. Como os engenheiros podem atestar, existem muitos tipos diferentes de chaves interruptoras, incluindo chaves alavanca, interruptores de balancim, interruptores pushbutton, micro-chaves, chaves fim de curso, atuadores magnéticos, reed switches e relés. Todos têm uma coisa em comum: eles repicam. É exatamente o que fazem.

Normalmente, esse repique tem pouco ou nenhum efeito no circuito, mas se o circuito digital for suficientemente rápido para detectar e responder a vários repiques, pode haver consequências graves. A tarefa de um engenheiro é evitar ou mitigar seus efeitos, ou ainda "conter o repique" do interruptor. Embora a indústria tenha praticado há muito tempo a contenção de repique via hardware, ela mudou mais recentemente para abordagens de contenção de repique baseadas em software. No entanto, há situações em que a contenção de repique via hardware é uma opção melhor.

Esse artigo descreve o repique e discute as abordagens de software e hardware para contê-lo. Em seguida, aponta para instâncias em que a contenção de repique via hardware é uma opção melhor, antes de mostrar como ela pode ser implementada. Exemplos de dispositivos de chaveamento e componentes de hardware para contenção de repique são apresentados por meio de amostras da NKK Switches, ON Semiconductor, Texas Instruments, Maxim Integrated e LogiSwitch.

O que é o repique de interruptores?

Quando um interruptor ou relé é comutado ou chaveado, o que um humano percebe como sendo uma resposta única instantânea cada vez que o dispositivo muda de estado pode realmente envolver 100 ou mais ações de fechar-e-abrir que persistem por vários milésimos de segundo antes do contato finalmente se estabelecer.

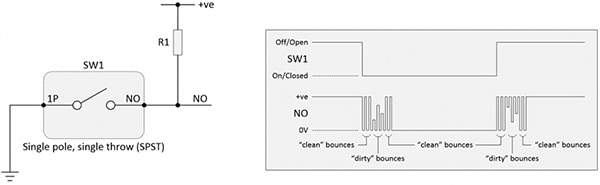

Por exemplo, considere uma chave alavanca de montagem em painel de um polo, curso único (SPST), normalmente aberta (NA) como uma M2011SS1W01 da NKK. Suponha que um lado desse interruptor, que pode ser considerado a entrada, está conectado ao terra (0 volts), enquanto o outro lado, que nesse caso é a saída, é conectado a uma fonte de alimentação de 5 volts (identificado como +ve) através de um resistor de pull-up (R1) (Figura 1).

Figura 1: no caso de uma chave alavanca SPST-NA, podem ocorrer repiques quando a chave é ativada e desativada. (Fonte da imagem: Max Maxfield)

Figura 1: no caso de uma chave alavanca SPST-NA, podem ocorrer repiques quando a chave é ativada e desativada. (Fonte da imagem: Max Maxfield)

Observe que o repique da chave pode ocorrer tanto quando ela é ativada (fechada) quanto desativada (aberta). Às vezes, os repiques podem migrar por todo o caminho entre as trilhas de alimentação, aqui considerados os estados lógicos 0 e 1. Nesse caso, esses são repiques "limpos". Por comparação, se o sinal atingir apenas uma tensão intermédia, esses são chamados de repiques "sujos".

No caso de uma chave alavanca de montagem em painel de um polo e curso duplo (SPDT), como a M2012SS1W01-BC da NKK, o repique pode ocorrer tanto no terminal normalmente aberto (NA) quanto no normalmente fechado (NF) (Figura 2). Nesse caso, apenas repiques "limpos" foram mostrados por simplicidade.

Figura 2: no caso de uma chave alavanca SPDT, podem ocorrer repiques tanto no terminal NA quanto no NF quando a chave é ativada e desativada. (Fonte da imagem: Max Maxfield)

Figura 2: no caso de uma chave alavanca SPDT, podem ocorrer repiques tanto no terminal NA quanto no NF quando a chave é ativada e desativada. (Fonte da imagem: Max Maxfield)

Em muitos casos, essa duração do sinal de repique é tal que não tem qualquer efeito. Os problemas surgem quando um interruptor é conectado a um equipamento eletrônico que é rápido o suficiente para detectar e responder a vários repiques. O que precisa é uma forma de conter o repique do sinal proveniente do interruptor antes que ele interfira no equipamento eletrônico.

Contenção de repique via software versus via hardware

Nas décadas de 1960 e 1970, a contenção de repique de interruptor foi implementada usando uma variedade de técnicas de hardware, desde simples circuitos de atraso tipo resistor-capacitor (RC) usados com interruptores SPST até funções mais sofisticadas de flip-flop SR (set/reset).

Mais recentemente, e em razão de muitos sistemas possuírem uma unidade microprocessadora (MPU) ou unidade microcontroladora (MCU), tornou-se comum utilizar técnicas de software para contar o repique do sinal proveniente de qualquer interruptor. Entretanto, a contenção de repique via software não é sempre a melhor abordagem. Há algumas aplicações que envolvem processadores pequenos, de baixo desempenho e com limitação de memória, com espaço limitado de código e/ou de ciclos de clock disponíveis para implementar rotinas de contenção de repique. Nesses casos, uma implementação via hardware pode ser uma solução melhor.

Além disso, muitos desenvolvedores de software não estão familiarizados com as características físicas dos interruptores, como o fato de que, além de variar de uma ativação para outra, as características de repique de um interruptor podem ser afetadas por condições ambientais como temperatura e umidade.

A questão da falta de conhecimento de comutação por parte dos desenvolvedores de software é agravada pelo fato de a literatura disponível sobre o repique dos interruptores ser muitas vezes confusa e contraditória. Por exemplo, é comum ler que um interruptor parará de repicar 1 milissegundo (ms) após sua ativação ou desativação. No entanto, o conhecido especialista em sistemas embarcados Jack Ganssle realizou testes empíricos em vários tipos de interruptores, ativando cada interruptor 300 vezes e registrando a quantidade mínima e máxima de repiques, tanto na abertura quanto no fechamento dos contatos. Ele registrou uma duração média de repique de 1,6 ms e uma duração máxima de repique de 6,2 ms. Algumas "melhores práticas" industriais e militares recomendam aguardar 20 ms após a ativação inicial antes de assumir que o interruptor parou de repicar; outros defendem aguardar 20 ms após o último repique detectado antes de iniciar quaisquer ações.

Além disso, existem muitos sistemas simples não baseados em processadores que também exigem que os interruptores tenham contenção de repique. Alguns exemplos de sistemas assim são um contador binário que aciona displays de sete segmentos contando pulsos de um relé; a entrada de gatilho de um temporizador 555 de disparo único que é utilizado como um controle de motor para uma porta ou portão; e uma máquina de estado finito baseada em registradores (FSM) que utiliza entradas chaveadas. Há também potenciômetros eletrônicos de ajuste (trimpots) com valores modificados por meio de entradas de interruptor (para cima, para baixo e, às vezes, armazenar) onde o repique do chave seria problemático.

Todos esses exemplos tornam claro que algum conhecimento de como realizar a contenção de repique via hardware pode ser útil para qualquer projetista ou desenvolvedor.

Hardware para conter o repique de um interruptor SPST com uma rede RC

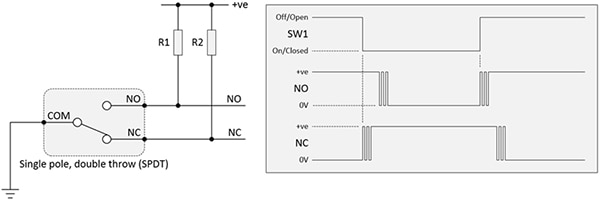

Uma das soluções mais simples de contenção de repique de interruptor baseada em hardware emprega uma rede capacitor-resistor (RC) em conjunto com um interruptor SPST. Há muitas variações desse circuito. Uma das implementações mais versáteis envolve dois resistores e um diodo (Figura 3).

Figura 3: ao utilizar uma rede RC para conter o repique de um interruptor SPST (acima), a inclusão do diodo (D1) força o capacitor (C1) a carregar através da resistência R1 e descarregar através da resistência R2. (Fonte da imagem: Max Maxfield)

Figura 3: ao utilizar uma rede RC para conter o repique de um interruptor SPST (acima), a inclusão do diodo (D1) força o capacitor (C1) a carregar através da resistência R1 e descarregar através da resistência R2. (Fonte da imagem: Max Maxfield)

Quando o interruptor é ativado (fechado), o capacitor C1 é descarregado através da resistência R2. Se o diodo D1 fosse omitido desse circuito, então ao desativar o interruptor (abrir), C1 seria carregado através de resistências (R1 + R2). No entanto, a presença de D1 implica que C1 será carregado apenas através de R1.

Em alguns casos, apenas a ativação do interruptor importa (ou seja, desencadeia ocorrência de ações), nesse caso, D1 pode ser omitido. No entanto, se as ações forem desencadeadas tanto na ativação quanto na desativação do interruptor, e se minimizar o atraso for uma preocupação, recomenda-se a inclusão de D1.

Observe as curvas de carga e descarga exponenciais exibidas pela tensão do capacitor VC. Não seria uma boa ideia injetar esse sinal diretamente na entrada de uma função lógica digital a jusante, que não compreenderia um sinal que vagueia na região indefinida entre os valores “bons” da lógica 0 e lógica 1. Em vez disso, esse sinal é injetado na entrada de um buffer com uma entrada de disparador Schmitt. Além disso, normalmente se usa um buffer de inversão, como um canal de um CD74HC14M96 da Texas Instruments, porque as funções de inversão comutam mais rápido do que suas contrapartes não inversoras.

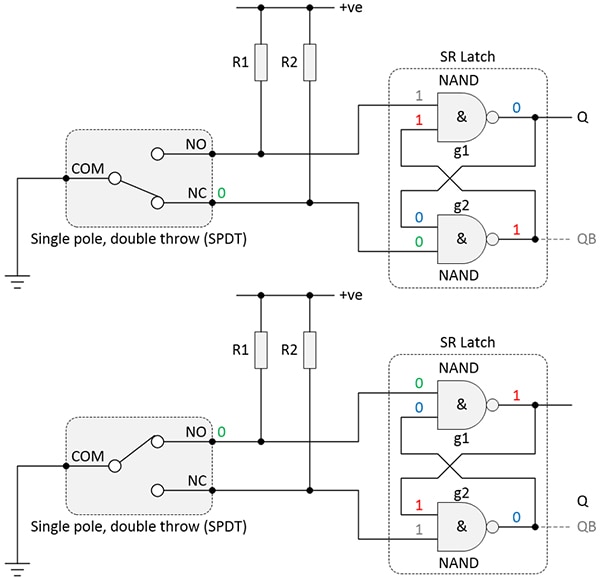

Contendo o repique de um interruptor SPDT com um flip-flop SR

No caso de um interruptor SPDT, uma solução comum de contenção de repique via hardware é empregar um flip-flop SR tipo latch. Desde que empresas como a IBM usaram essa técnica para os painéis de interruptores de seus computadores mainframe por volta dos anos 60, essa abordagem tem sido considerada como o crème de la crème das soluções simples de contenção de repique via hardware. Tal flip-flop pode ser feito usando duas portas NAND de duas entradas, realimentadas; por exemplo, empregando dois canais de um CI NAND quádruplo de duas entradas SN74HC00DR da Texas Instruments (Figura 4).

Figura 4: o uso de um flip-flop SR baseado em NAND para contenção de repique de um interruptor SPDT é uma solução via hardware muito eficaz. (Fonte da imagem: Max Maxfield)

Figura 4: o uso de um flip-flop SR baseado em NAND para contenção de repique de um interruptor SPDT é uma solução via hardware muito eficaz. (Fonte da imagem: Max Maxfield)

Quando o terminal NF do interruptor é conectado ao terra, como mostrado na metade superior da Figura 4, força a saída da porta g2 para a lógica 1. Por sua vez, as duas lógicas 1 nas entradas da porta g1 forçam sua saída para a lógica 0. Por comparação, quando o terminal NA do interruptor é conectado ao terra, como mostrado na metade inferior da Figura 4, força a saída da porta g1 para a lógica 1. Por sua vez, as duas lógicas 1 nas entradas da porta g2 forçam sua saída para a lógica 0.

O motivo pelo qual esse circuito funciona tão bem é que quando ambas as entradas estão nos seus estados inativos de lógica 1, o flip-flop SR memoriza o seu valor anterior. Lembre-se de que, conforme ilustrado na Figura 2, quando um interruptor SPDT é comutado, independente de qual dos terminais é conectado ao terra — naquele momento no tempo — ocorre primeiro um repique. Como esses repiques estão entre seu valor original (lógica 0) e seu novo valor (lógica 1), eles não têm efeito no estado atual do flip-flop SR. Só depois que esse terminal para de repicar é que a sua contraparte começa a repicar, momento em que o flip-flop SR muda de estado.

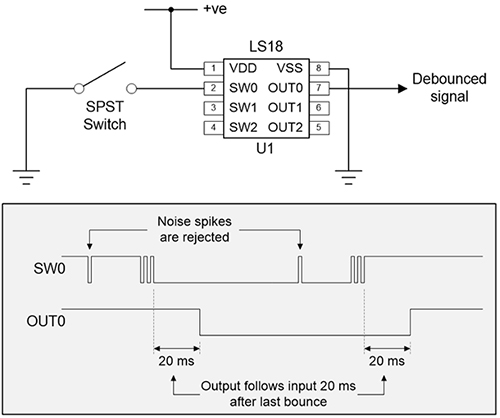

Contendo o repique de um interruptor SPST com um dispositivo dedicado

Um problema com a solução anterior é que muitos projetistas preferem usar interruptores SPST porque geralmente custam menos que os SPDTs. Existem vários dispositivos de contenção de repique SPST dedicados bem conhecidos no mercado, como o MC14490DWG da ON Semiconductor e o MAX6818EAP+T da Maxim Integrated.

Outro fabricante, a LogiSwitch, oferece soluções de contenção de repique em pacotes de três, seis e nove canais, tanto em encapsulamentos para montagem em furo passante quanto em superfície (SMD). Por exemplo, considere um circuito usando um dispositivo LS18-S da LogiSwitch (Figura 5).

Figura 5: usando um chip LS18-S dedicado de três canais para conter o repique de um interruptor SPDT (dispositivos de seis e nove canais também estão disponíveis). (Fonte da imagem: Max Maxfield)

Figura 5: usando um chip LS18-S dedicado de três canais para conter o repique de um interruptor SPDT (dispositivos de seis e nove canais também estão disponíveis). (Fonte da imagem: Max Maxfield)

Como todos os membros da família LogiSwitch, o LS18-S suporta uma faixa de tensão operacional de 2,5 a 5,5 volts (o valor da tensão de alimentação não afeta o tempo de resposta do dispositivo). Além disso, ao contrário de algumas das outras soluções de CIs dedicados, os dispositivos de contenção de repique da LogiSwitch não requerem componentes adicionais, como um clock externo, uma rede de temporização RC ou resistores de pull-up nas entradas ou saídas.

O LS18-S usa a tecnologia adaptativa patenteada NoBounce da LogiSwitch, que oferece um alto nível de imunidade a ruído. Picos de ruído com menos de 20 ms de duração são impedidos de iniciar ou terminar um ciclo, e as saídas são retardadas durante um período de 20 ms após o repique final do interruptor, tanto na ativação quanto na libertação, independentemente da duração do repique.

Conclusão

Existem muitos tipos diferentes de interruptores, incluindo chaves alavanca, interruptores de balancim e interruptores pushbutton, e todos podem repicar. Se não for contido, o repique do interruptor pode fazer com que os microprocessadores e outros circuitos eletrônicos enxerguem uma única ativação do interruptor como sendo múltiplos eventos.

O sinal de repique de um interruptor é frequentemente contido usando um software sendo executado por um microcontrolador. Embora esta seja uma solução de baixo custo, como mostrado, pode não ser a melhor opção em todos os casos, incluindo sistemas baseados em microcontroladores de desempenho e memória limitados, desenvolvedores de software sem experiência em problemas relacionados a interruptores ou sistemas implementados sem um microcontrolador.

Como alternativa, a contenção de repique pode ser realizada via hardware usando uma variedade de abordagens que vão desde redes resistor-capacitor, flip-flops SR tipo latch até circuitos integrados dedicados.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.