Use módulos com amplificadores integrados para remover a “magia negra” dos projetos ADC de alta velocidade

Contributed By DigiKey's North American Editors

2021-04-29

Os projetistas de sistemas como aquisição de dados, hardware in the loop (HiL) e analisadores de potência precisam de uma cadeia de conversores de sinais analógicos que possam alcançar alta resolução e alta precisão a taxas de amostragem muito altas, muitas vezes até 15 mega amostras por segundo (MSPS). Entretanto, projetos analógicos de alta velocidade podem parecer "magia negra" para muitos projetistas, especialmente quando confrontados com uma série de parasitas ocultos que impactam a integridade do sinal.

Por exemplo, os projetos típicos são discretos e contêm vários CIs e componentes, incluindo um amplificador totalmente diferencial (FDA), um filtro passa-baixa (LPF) de primeira (1ª) ordem, uma referência de tensão e um conversor analógico-digital de alta velocidade e alta resolução (ADC). Os parasitas capacitivos e resistivos estão dentro e ao redor do amplificador controlador do ADC (o FDA), do filtro de entrada do ADC, e do ADC.

Eliminar, reduzir ou mitigar os efeitos parasitas é um desafio. Requer um alto grau de habilidade e pode exigir muitos ciclos de projeto de circuitos e iterações de layout de placas de circuito impresso, comprometendo cronogramas e orçamentos de projeto. O que é necessário é uma solução mais completa e integrada que resolva muitos desses problemas de projeto.

Este artigo descreverá um circuito discreto de aquisição de dados e problemas de layout relacionados, e então introduzirá um módulo integrado que contém um ADC de alta resolução, registrador de aproximação sucessiva de alta velocidade (SAR) com um FDA front-end. O artigo mostra como o módulo completo ADAQ23875 da Analog Devices e sua placa de desenvolvimento associada supera dores de cabeça do projeto de alta velocidade, simplificando e acelerando o processo de projeto enquanto ainda alcança os resultados necessários de alta resolução e conversão em alta velocidade.

Caminho do sinal de aquisição de dados em alta velocidade

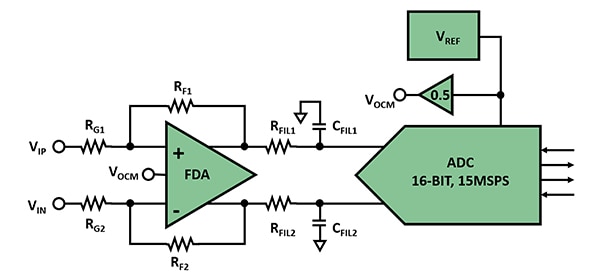

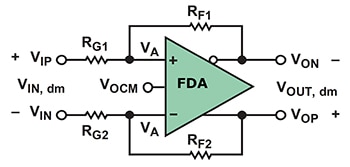

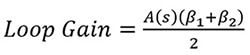

Os ADCs de alto desempenho usam entradas diferenciais para melhorar o desempenho geral, balanceando os sinais de entrada e rejeitando ruídos e interferências do modo comum. Um amplificador do ADC analógico atinge o desempenho ideal quando as entradas para o amplificador do ADC analógico e ADC são totalmente diferenciais (Figura 1). O uso de uma interface serial de sinalização diferencial de baixa tensão (LVDS) (à direita) permite que o sistema funcione a velocidades extremamente altas para atender às aplicações de aquisição de dados, HiL e analisadores de potência.

Figura 1: Um sistema de aquisição de dados de alta frequência com um filtro analógico de 1ª ordem do FDA e entrada diferencial SAR-ADC com uma interface serial LVDS de alta velocidade. (Fonte da imagem: Bonnie Baker)

Figura 1: Um sistema de aquisição de dados de alta frequência com um filtro analógico de 1ª ordem do FDA e entrada diferencial SAR-ADC com uma interface serial LVDS de alta velocidade. (Fonte da imagem: Bonnie Baker)

A configuração na Figura 1 desempenha muitas funções essenciais, incluindo a escala de amplitude, conversão de um terminal simples para o diferencial, função de buffer, ajuste de offset/compensação em modo comum e filtragem.

Tecnologia do amplificador FDA

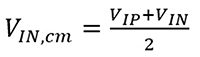

O funcionamento do amplificador ADC com realimentação de tensão do FDA é como um amplificador convencional, exceto por duas diferenças. Primeiro, o FDA tem uma saída diferencial com um terminal de saída negativa adicional (VON). Em segundo lugar, tem um terminal de entrada adicional (VOCM) que define a tensão em modo comum de saída (Figura 2).

Figura 2: o FDA tem duas entradas com malhas de realimentação e controle de tensão (VOCM) da tensão de saída em modo comum. Esta configuração cria uma tensão independente de entrada diferencial (VIN, dm) e de saída diferencial (VOUT, dm). (Fonte da imagem: Analog Devices)

Figura 2: o FDA tem duas entradas com malhas de realimentação e controle de tensão (VOCM) da tensão de saída em modo comum. Esta configuração cria uma tensão independente de entrada diferencial (VIN, dm) e de saída diferencial (VOUT, dm). (Fonte da imagem: Analog Devices)

Internamente, o FDA tem três amplificadores: dois na entrada e o terceiro atuando como o estágio de saída. A realimentação negativa (RF1, RF2) e o alto ganho em malha aberta dos dois amplificadores de entrada internos ditam o comportamento dos terminais de entrada, VA+ e VA-, para serem virtualmente iguais. Em vez de uma saída com terminal simples, o FDA produz uma saída diferencial balanceada entre VOP e VON, com uma tensão em modo comum de VOCM.

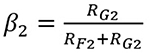

Os sinais diferenciais de entrada (VIP e VIN) são iguais em amplitude e opostos em fase em torno de uma tensão de referência em modo comum (VIN, cm) com um sinal de entrada balanceado. As equações 1 e 2 mostram como calcular a tensão de entrada em modo diferencial (VIN, dm) e a tensão de entrada em modo comum (VIN, cm).

![]() Equação 1

Equação 1

Equação 2

Equação 2

As equações 3 e 4 fornecem as definições do modo diferencial e comum de saída.

![]() Equação 3

Equação 3

![]() Equação 4

Equação 4

Observe a inclusão do VOCM na Equação 4.

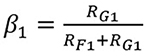

Como nos circuitos de amplificação típicos, o ganho do sistema FDA depende dos valores RGx e RFx. As equações 5 e 6 definem os dois fatores de realimentação de entrada, β1 e β2, para o FDA.

Equação 5

Equação 5

Equação 6

Equação 6

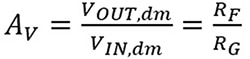

Quando β1 for igual a β2, a Equação 7 dará o ganho ideal de malha fechada para o FDA.

Equação 7

Equação 7

VOUT, dm fornece uma idéia do desempenho dos descasamentos resistivos. A equação geral de malha fechada para VOUT, dm inclui VIP, VIN, β1, β2 e VOCM. A equação 8 mostra a fórmula para VOUT, dm com o ganho de tensão do amplificador em malha aberta mostrado como A(s).

![VOUT,dm = [2 / β1 + β2] [VOCM(β1-β2)+VIP(1-β1)-VIN(1-β2) / 1 + 2/ A(S)(β1+β2)] Equação 8](http://sc-a.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2021/April/Use%20Modules%20with%20Integrated%20Amplifiers%20High-Speed%20ADC%20Design/article-2021april-use-modules-with-integrated-equation8.jpg?la=en&ts=fc1271d3-3f9d-4f4e-8cbc-609177a3d0b0) Equação 8

Equação 8

Quando β1 ≠ β2, o erro da tensão diferencial de saída (VOUT, dm) dependerá principalmente da VOCM. Este resultado indesejável produz um offset e um excesso de ruído na saída diferencial. Se β1 = β2 ≡ β, a Equação 8 se torna a Equação 9.

![VOUT,dm / VIN,dm = [RF/RG] [1 / 1 + 1/A(S)(β)] Equação 9](http://sc-c.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2021/April/Use%20Modules%20with%20Integrated%20Amplifiers%20High-Speed%20ADC%20Design/article-2021april-use-modules-with-integrated-equation9.jpg?la=en&ts=f057ce79-c262-4b25-a568-5a964b24c988) Equação 9

Equação 9

Os dois componentes do balanço de saída são a amplitude e a fase. O balanço de amplitude mede se as duas amplitudes de saída são iguais; o ideal é que elas correspondam exatamente. O balanço de fase mede a proximidade das diferenças de fase entre as duas saídas com o ideal igualando 180°.

As considerações de estabilidade do FDA são as mesmas de um amplificador operacional padrão. A especificação chave é a margem de fase. As fichas técnicas dos produtos fornecem a margem de fase de uma determinada configuração do amplificador; no entanto, os efeitos parasitas do layout da placa de circuito podem reduzir significativamente a estabilidade. No caso de um amplificador de realimentação negativa de tensão, é bastante simples: a estabilidade depende do seu ganho de malha, A(s) × β, sinal e magnitude. O FDA, em contraste, tem dois fatores de realimentação. As equações 8 e 9 têm o ganho de malha em seus denominadores. A equação 10 descreve o ganho de malha para o caso do fator de realimentação descasado (β1 ≠ β2).

Equação 10

Equação 10

A atenuação de todos os erros acima depende do tedioso e caro processo de casamento com os resistores discretos RG1, RG2, RF1 e RF2.

Desempenho combinado do FDA e ADC

O FDA, resistores discretos, filtro de 1ª ordem e combinação ADC contam a história sobre a relação sinal/ruído (SNR), distorção harmônica total (THD), sinal/ruído e distorção (SINAD) e faixa dinâmica livre de espúrios (SFDR) que acrescentam às características de desempenho do FDA na precisão e resolução geral do circuito. As especificações combinadas incluem o SNR, THD, SINAD e SFDR. O FDA tem numerosas especificações que afetam essas especificações de frequência, tais como largura de banda, ruído da tensão de saída, distorção, estabilidade e tempo de assentamento, tudo isso afeta o desempenho do ADC. O ADC tem seu próprio conjunto de especificações. O desafio significativo é selecionar o FDA apropriado para corresponder ao ADC.

Layout da placa

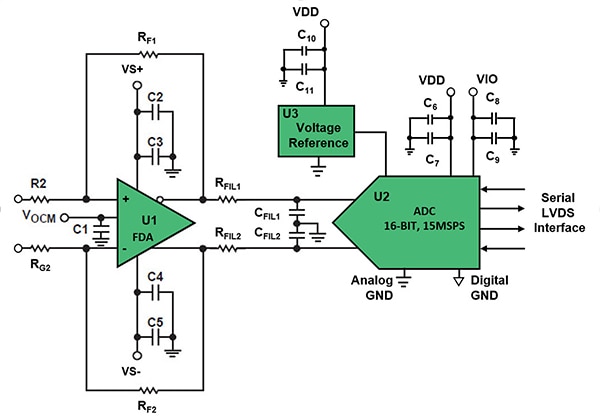

O layout da placa de circuito é a última etapa no processo de design. Infelizmente, o layout pode ser uma etapa de projeto negligenciada, resultando em um design de placa ruim que pode comprometer ou tornar o circuito inútil. Este circuito discreto completo tem três circuitos integrados, seis resistores e vários capacitores de desacoplamento (Figura 3).

Figura 3: FDA, SAR-ADC e LPF de 1ª ordem com capacitores de desacoplamento da fonte de alimentação. (Fonte da imagem: Analog Devices)

Figura 3: FDA, SAR-ADC e LPF de 1ª ordem com capacitores de desacoplamento da fonte de alimentação. (Fonte da imagem: Analog Devices)

Na Figura 3, os elementos parasitas que minam o desempenho do circuito de alta velocidade são a capacitância e indutância parasitária da placa de circuito impresso. Os culpados são as ilhas dos componentes, trilhas, vias e terra em paralelo com os planos de alimentação. Estas capacitâncias e indutâncias são especialmente perigosas nos nós de soma do amplificador, onde introduzem pólos e zeros na resposta de realimentação, causando picos e instabilidade.

Solução integrada

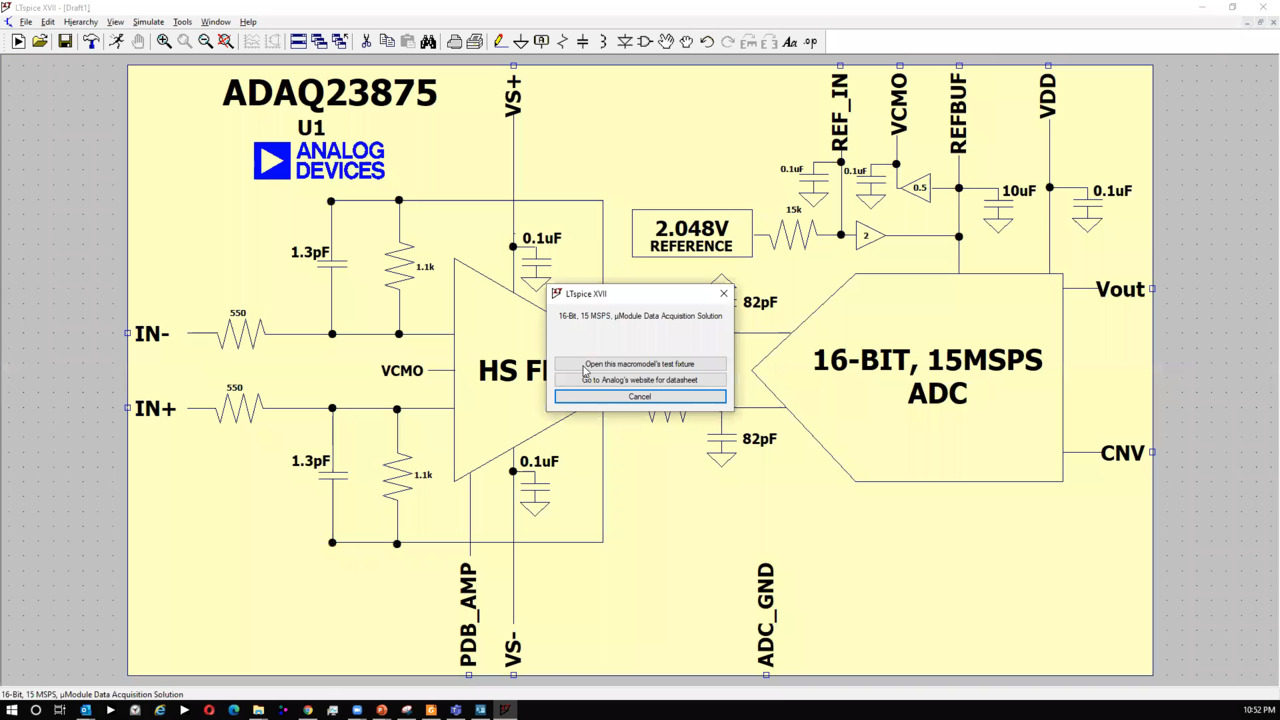

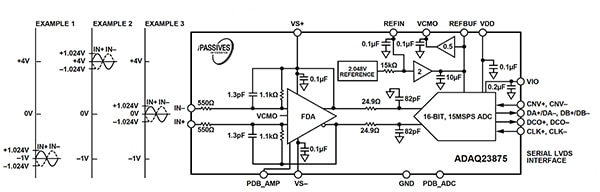

Os conversores SAR podem oferecer um FDA, componentes passivos cruciais, filtros de 1ª ordem, uma referência de tensão e capacitores de desacoplamento para melhorar a resolução efetiva. Por exemplo, o ADAQ23875 da Analog Devices é um módulo de aquisição de dados de 16 bits e 15 MSPS com todos estes elementos (Figura 4). Como tal, reduz o ciclo de desenvolvimento de sistemas de medição de precisão ao transferir a carga de projeto da seleção de componentes, otimização e layout do projetista para o circuito integrado.

Figura 4: O ADAQ23875 simplifica o projeto de ADCs de alta velocidade através da combinação de um FDA, filtro de 1ª ordem e SAR-ADC em um único módulo, suportado por resistores de ganho ajustados a laser ao redor do FDA, bem como capacitores de desacoplamento no chip. (Fonte da imagem: Analog Devices)

Figura 4: O ADAQ23875 simplifica o projeto de ADCs de alta velocidade através da combinação de um FDA, filtro de 1ª ordem e SAR-ADC em um único módulo, suportado por resistores de ganho ajustados a laser ao redor do FDA, bem como capacitores de desacoplamento no chip. (Fonte da imagem: Analog Devices)

Os componentes resistivos passivos no chip possuem características superiores de correspondência e deriva para minimizar fontes de erros dependentes de parasitas e oferecer desempenho otimizado para garantir o casamento muito próximo de β1 e β2. O casamento destes ganhos de malha ajuda a criar a compensação de ±1 mV do módulo e especificações de ruído RMS total de 91,6 µVRMS.

A referência de tensão de 2,048 volts de banda proibida tem baixo ruído e baixa deriva (20 partes por milhão por grau Celsius (ppm/°C)) para suportar o sistema FDA e ADC de 16 bits. Em conjunto com o FDA, estas especificações se traduzem em precisão SNR de 90 dB do SAR-ADC e deriva de ganho de ±1 ppm/°C. O pino VOCM do FDA usa os 2,048 volts de referência para fornecer a tensão de saída em modo comum.

Um buffer interno amplifica a referência de 2,048 volts por dois para criar 4,096 volts para a tensão de referência do ADC. A diferença de tensão entre a referência do ADC e o GND determina o fundo de escala da faixa de entrada do SAR-ADC ADAQ23875. Além disso, o ADAQ23875 tem um capacitor de desacoplamento no chip de 10 μF entre o buffer de referência e o GND para absorver picos de carga da conversão de referência do SAR-ADC e aliviar as limitações de layout do projeto em componentes discretos.

Como mostra a Figura 4, no FDA, a tensão de entrada em modo comum é independente da tensão de saída em modo comum. Nos exemplos de um a três, as tensões de alimentação são:

VS+ = 7 volts (tensão de alimentação positiva do FDA)

VS- = -2 volts (tensão de alimentação negativa do FDA)

VDD = +5 volts (tensão de alimentação do ADC)

VIO = 2,5 volts (tensão de alimentação de saída analógica e digital)

O exemplo 1 mostra uma faixa de tensão de entrada de ±1,024 volts com uma tensão de entrada em modo comum de -1 volts. O FDA aplica um ganho de 2 volts/volt a esses sinais, e o nível do FDA desloca a tensão de saída pelo valor em VCMO ou 2,048 volts. O processo apresenta uma faixa de sinal de ±2,048 volts com uma tensão em modo comum da VCMO de 2,48 volts na saída do FDA. A frequência de corte do filtro de 1ª ordem é 1/(2pR x C) hertz (Hz) ou ~78 megahertz (MHz). A faixa de entrada do sinal para o ADC é de ±2,048 volts, com uma tensão de modo comum de +2,048 volts.

O ADAQ23875 tem uma interface digital LVDS com modos de saída de uma ou duas pistas, permitindo ao usuário otimizar a taxa de dados da interface de cada aplicação. A tensão de alimentação digital para a interface é VIO.

O ADAQ23875 tem quatro pinos de alimentação: um interno ao núcleo ADC (VDD), um da interface de entrada/saída digital (VIO), um para alimentação positiva (VS+) e um para alimentação negativa (VS-) do FDA. Para aliviar os problemas de layout da placa de circuito impresso, todos os pinos de alimentação têm capacitores de desacoplamento de 0,1 mF ou 0,2 mF no chip. É necessário colocar capacitores cerâmicos de boa qualidade de 2,2 μF (0402, X5R) para desacoplamento sobre a placa de circuito impresso na saída dos reguladores LDO. Estes reguladores abastecem as trilhas de alimentação do micromódulo (VDD, VIO, VS+ e VS-) para minimizar a suscetibilidade à interferência eletromagnética (EMI) e reduzir o efeito sobre falhas na linha de alimentação. Todos os outros capacitores de desacoplamento necessários estão dentro do ADAQ23875, melhorando a taxa geral de rejeição da fonte de alimentação do subsistema (PSRR), e economizando espaço e custo extra da placa. Para usar a referência interna e o buffer interno de referência, desacople o pino REFIN para GND com um capacitor cerâmico de 0,1 μF.

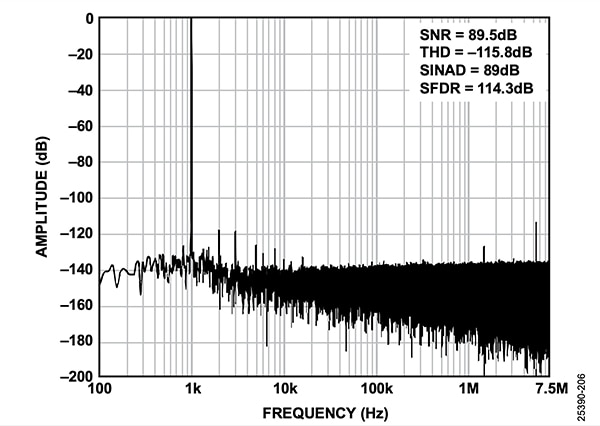

O módulo ADAQ23875 elimina as dores de cabeça de selecionar o FDA apropriado e a rede resistiva do ADC, enquanto ainda garante alto desempenho e especificações rigorosas para SNR, THD, SINAD e SFDR (89,5 dB, -115,8 dB, 89 dB, e 114,3 dB, respectivamente) (Figura 5). Normalmente, a coleta das especificações do sistema fica a cargo do projetista. A abordagem de sistema do ADAQ23875 ajuda os projetistas a alcançar estas especificações de forma mais eficiente.

Figura 5: O módulo ADAQ23875 cria as especificações SNR, THD, SINAD, SFDR que passam pelo FDA no chip, filtro de 1ª ordem e SAR-ADC. (Fonte da imagem: Analog Devices)

Figura 5: O módulo ADAQ23875 cria as especificações SNR, THD, SINAD, SFDR que passam pelo FDA no chip, filtro de 1ª ordem e SAR-ADC. (Fonte da imagem: Analog Devices)

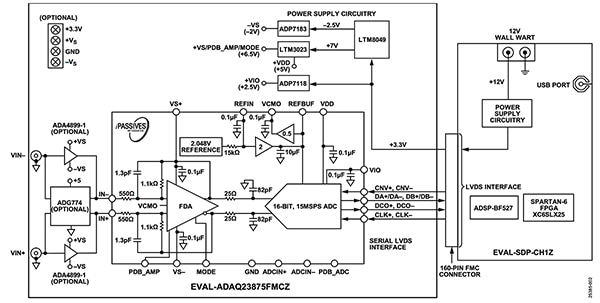

A figura 5 mostra os resultados dos testes SNR, THD, SINAD e SFDR para um sinal de entrada diferencial de 1 kHz no ADAQ23875. Para uma aplicação específica, a placa EVAL-ADAQ23875FMCZ para o ADAQ23875 possui software para auxiliar nas avaliações de dispositivos, incluindo programação de dispositivos, forma de onda, histograma e captura FFT. Os projetistas podem conectar a placa de avaliação à plataforma de demonstração do sistema EVAL-SDP-CH1Z da ADI para energizar, e permitir o controle da placa de avaliação por um PC através da porta USB do SDP-CH1Z (Figura 6).

Figura 6: A placa de avaliação ADAQ23875FMCZ (esquerda) conectada à placa da plataforma de demonstração do sistema (EVAL-SDP-CH1Z) (direita), permitindo o controle da placa de avaliação através da porta USB de um PC. (Fonte da imagem: Analog Devices)

Figura 6: A placa de avaliação ADAQ23875FMCZ (esquerda) conectada à placa da plataforma de demonstração do sistema (EVAL-SDP-CH1Z) (direita), permitindo o controle da placa de avaliação através da porta USB de um PC. (Fonte da imagem: Analog Devices)

O software da placa de avaliação, plugin ACE para a placa ADAQ23875 1.2021.8300 [Fev 18 21] e software de instalação ACE 1.21.2994.1347 [Fev 08 21], permite que o usuário configure o valor de sobreamostra de cada canal, faixa de entrada, número de amostras e seleção ativa de canais. Além disso, este software também torna possível salvar e abrir arquivos de dados de teste.

Conclusão

Para superar os desafios do projeto analógico de alta velocidade e oferecer o melhor desempenho geral de aquisição de dados, os projetistas podem recorrer ao módulo ADAQ23875. Este é um sistema completo de conversão de alta velocidade que inclui um FDA, um filtro passa-baixa de 1ª ordem, SAR-ADC e uma série de capacitores de desacoplamento que amplificam os sinais de excitação e fornecem os sinais de acionamento apropriados, bem como a filtragem e o retorno de alimentação dos sinais secundários. Um módulo altamente integrado, o módulo do sistema de aquisição de dados ADAQ23875 permite o projeto de "magia negra" analógica com uma solução completa do FDA ao SAR-ADC para aquisição de dados de alta velocidade, hardware in the loop (HiL) e analisadores de potência.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.