Uso de um transceptor de RF ágil em um sistema de comunicação SDR adaptável para o setor aeroespacial e de defesa

Contributed By DigiKey's North American Editors

2023-11-30

Os projetistas de sistemas aeroespaciais e de defesa (ADEF) enfrentam uma demanda incessante por sistemas de comunicação mais compactos e de menor potência, capazes de responder com agilidade a um ambiente de sinais dinâmicos. Indo além das arquiteturas de rádio tradicionais, a tecnologia de rádio definido por software (SDR) pode ajudar a atender aos requisitos em rápida mudança dos rádios ADEF, mas a implementação do SDR vem apresentando vários desafios para atender aos requisitos funcionais e à necessidade de redução de tamanho, peso e potência (SWaP).

Este artigo descreve uma solução SDR mais eficaz da Analog Devices que pode simplificar o projeto de sistemas de comunicação de baixa potência, compactos e ágeis sem comprometer o desempenho.

Desafios emergentes geram requisitos mais exigentes

Os projetistas enfrentam uma demanda por comunicações mais eficazes em uma série crescente de aplicações industriais e de missão crítica, incluindo comunicações seguras de rádio, radar adaptável, guerra eletrônica e navegação GPS aprimorada. Esses novos desafios geram a necessidade de uma operação de banda larga aprimorada, maior faixa dinâmica, maior agilidade de frequência e reconfigurabilidade. No entanto, esses requisitos funcionais mais exigentes podem entrar em conflito com a necessidade de um SWaP mais baixo, à medida que os sistemas de comunicação passam para plataformas menores alimentadas por bateria, incluindo veículos aéreos não tripulados (SANT) e unidades portáteis.

As soluções de projeto baseadas em arquiteturas tradicionais de rádio super-heteródino discreto oferecem alto desempenho, ampla faixa dinâmica e ruído espúrio mínimo. Para os projetistas, o desafio de isolar o sinal desejado da frequência intermediária (IF) no centro dessa abordagem, geralmente resulta em projetos complexos com alto SWaP e pouca ou nenhuma reconfigurabilidade (Figura 1).

Figura 1: As arquiteturas tradicionais de rádio super-heteródino podem atender às metas de desempenho, mas sua complexidade as impede de atender às metas emergentes de SWaP mínimo. (Fonte da imagem: Analog Devices)

Figura 1: As arquiteturas tradicionais de rádio super-heteródino podem atender às metas de desempenho, mas sua complexidade as impede de atender às metas emergentes de SWaP mínimo. (Fonte da imagem: Analog Devices)

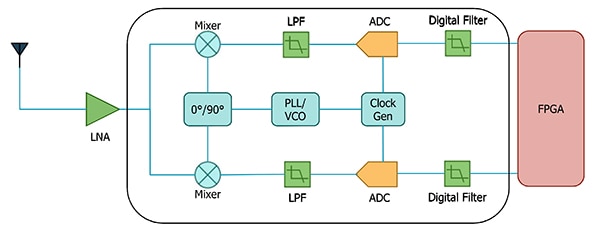

Por outro lado, as arquiteturas de conversão direta (zero-IF) reduzem os requisitos de filtragem e a necessidade de conversores analógico-digitais (ADCs) de largura de banda muito alta, resultando em um projeto mais simples que pode ser implementado em um único chip (Figura 2).

Figura 2: As arquiteturas de rádio Zero-IF podem atender à necessidade de maior desempenho e menor SWaP, mas o isolamento do sinal é um desafio. (Fonte da imagem: Analog Devices)

Figura 2: As arquiteturas de rádio Zero-IF podem atender à necessidade de maior desempenho e menor SWaP, mas o isolamento do sinal é um desafio. (Fonte da imagem: Analog Devices)

Apesar de suas vantagens aparentes, a arquitetura de conversão direta apresenta seus próprios desafios de implementação que limitaram sua adoção generalizada. Nessa arquitetura, o sinal é convertido em uma portadora de radiofrequência (RF) na frequência do oscilador local (LO), mas os erros de offset da corrente contínua (CC) e a fuga do LO podem resultar na propagação de erros pela cadeia de sinais. Além disso, as diferenças nos caminhos do sinal, mesmo dentro do mesmo chip, podem introduzir um ganho ou um desalinhamento de fase do sinal em fase (I) e em quadratura (Q), resultando em um erro de quadratura que pode comprometer o isolamento do sinal.

A tecnologia SDR oferece o potencial de superar as limitações das arquiteturas tradicionais de rádio, mas poucas soluções podem atender aos requisitos mais amplos associados às aplicações ADEF. Usando o transceptor de RF ADRV9002 da Analog Devices, os desenvolvedores podem facilmente atender à necessidade de maior desempenho e funcionalidade com o SWaP mais baixo exigido nessas aplicações.

A funcionalidade integrada oferece desempenho otimizado com SWaP reduzido

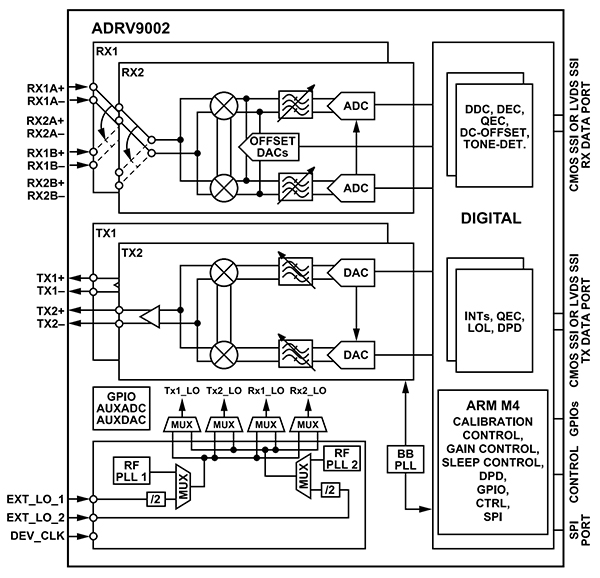

Suportando uma faixa de frequência de 30 megahertz (MHz) a 6.000 MHz, o ADRV9002 é um transceptor altamente integrado que contém todas as funcionalidades digitais, de sinal misto e de RF necessárias para suportar uma ampla gama de requisitos de aplicações. Capaz de operar tanto em duplex por divisão de tempo (TDD) quanto em duplex por divisão de frequência (FDD), o dispositivo apresenta subsistemas separados de receptor e transmissor de conversão direta em canal duplo que incluem filtros digitais programáveis, correção de offset CC e correção de erro em quadratura (QEC).

Em seu subsistema de sintetizador no chip, o ADRV9002 apresenta dois caminhos distintos da malha de captura de fase (PLL): um para o caminho de RF de alta frequência e outro para os clocks digitais e os clocks de amostragem do conversor. Por fim, o bloco de processamento de sinal digital do dispositivo inclui um processador Arm® M4 incorporado que lida com funções de autocalibração e controle (Figura 3).

Figura 3: O transceptor de RF ADRV9002 integra subsistemas duplos de recepção (RX) e transmissão (TX). (Fonte da imagem: Analog Devices)

Figura 3: O transceptor de RF ADRV9002 integra subsistemas duplos de recepção (RX) e transmissão (TX). (Fonte da imagem: Analog Devices)

Capaz de operar no modo zero-IF ou no modo baixa-IF para aplicações sensíveis a ruídos-fase, o ADRV9002 apresenta subsistemas de transmissor e receptor que oferecem cadeias de sinal completas. Cada subsistema de transmissor fornece um par de conversores digitais para analógicos (DAC), filtros e misturadores que recombinam os sinais I e Q e os modulam na frequência da portadora para transmissão.

Cada subsistema de receptor integra uma rede resistiva de entrada para controle de ganho que alimenta um misturador passivo em modo de corrente. Por sua vez, um amplificador de transimpedância converte a saída de corrente do misturador em um nível de tensão que é digitalizado por um ADC com alta faixa dinâmica. Durante os intervalos disponíveis do transmissor na operação TDD ou em aplicações FDD, em que apenas um sistema receptor é usado, as entradas de receptor não utilizadas podem ser usadas para monitorar os canais do transmissor quanto à fuga do LO e QEC, ou as entradas de receptor não utilizadas podem ser usadas para monitorar os níveis do sinal de saída do amplificador de potência (PA).

O último recurso entra em ação na característica de pré-distorção digital (DPD) integrado do ADRV9002, que usa seus níveis de sinal do PA monitorados para aplicar a pré-distorção apropriada necessária para linearizar a saída. Esse recurso permite que o ADRV9002 acione o PA mais próximo para saturação, otimizando sua eficiência.

Ajuste de potência e desempenho

O dispositivo ADRV9002 oferece uma solução totalmente integrada em um invólucro em escala de chip (CSP) de 196 esferas BGA (ball grid array), além de minimizar o tamanho e o peso dos sistemas de comunicação SDR ADEF. Para ajudar os desenvolvedores a otimizar ainda mais o consumo de energia, o ADRV9002 integra vários recursos projetados especificamente para encontrar um equilíbrio adequado entre desempenho e potência.

Ao de nível de bloco, os desenvolvedores podem implementar o escalonamento de potência em blocos individuais de caminho de sinal para tolerar o desempenho reduzido em prol de um menor consumo de energia. Além disso, os blocos nos quadros de recepção (RX) e transmissão (TX) do TDD podem ser desativados para sacrificar os tempos de resposta RX/TX ou TX/RX a fim de reduzir o consumo de energia. Para ajudar ainda mais a capacidade dos desenvolvedores de otimizar a potência em relação ao desempenho, cada subsistema do receptor ADRV9002 inclui dois pares de ADCs. Um par inclui ADCs sigma-delta de alto desempenho, enquanto o segundo par pode ser substituído quando o consumo de energia for crítico.

Para aplicações caracterizadas por períodos prolongados de inatividade, o modo de monitor RX do ADRV9002 pode ser empregado. Nesse modo, o ADRV9002 alterna entre um estado de suspensão de potência mínima e um estado de detecção em um ciclo de trabalho programado. No estado de detecção, o dispositivo ativa um receptor e tenta adquirir um sinal em uma largura de banda e uma frequência RX LO programadas pelo desenvolvedor. Se o dispositivo medir o nível de potência do sinal acima do limite programado, o dispositivo sai do modo monitor e os blocos do ADRV9002 são energizados para lidar com o sinal desejado.

Prototipagem e desenvolvimento rápidos

Para ajudar os engenheiros a passar rapidamente para a avaliação, prototipagem e desenvolvimento, a Analog Devices oferece amplo suporte de hardware e software para sistemas baseados no ADRV9002.

Para suporte de hardware, a Analog Devices oferece um par de placas baseadas em ADRV9002:

- ADRV9002NP/W1/PCBZ para aplicações de banda baixa operando na faixa de 30 MHz a 3 gigahertz (GHz)

- ADRV9002NP/W2/PCBZ para aplicações de banda alta na faixa de 3 a 6 GHz

Equipadas com conectores FMC, essas placas suportam o ADRV9002 na placa com regulagem de potência e interfaces de hardware, bem como distribuição de clock e sincronização multichip (MCS). As placas se conectam por meio de seu conector FMC a uma placa-mãe FPGA, como a placa de teste ZCU102 da AMD, para controle de potência e da aplicação.

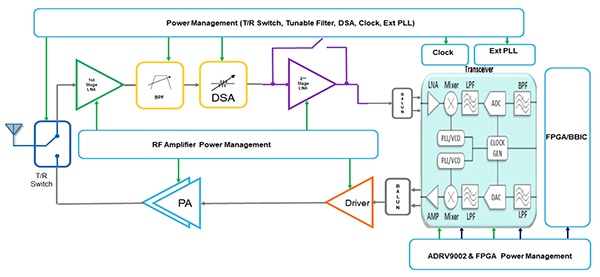

A Analog Devices fornece um esquema completo e uma lista de materiais (BOM) para suas placas de rádio ADRV9002NP em seu pacote de suporte. O esquema e a lista de materiais fornecem um ponto de partida eficaz para o desenvolvimento de hardware personalizado para a maioria das aplicações. Algumas aplicações exigem um front-end de RF adicional para atender a requisitos específicos de condicionamento de sinal. Para essas aplicações, os desenvolvedores precisam apenas de alguns componentes adicionais para concluir seu projeto (Figura 4).

Figura 4: O transceptor ADRV9002 altamente integrado permite que os desenvolvedores implementem rapidamente projetos especializados. (Fonte da imagem: Analog Devices)

Figura 4: O transceptor ADRV9002 altamente integrado permite que os desenvolvedores implementem rapidamente projetos especializados. (Fonte da imagem: Analog Devices)

Neste exemplo, os desenvolvedores podem implementar rapidamente um front-end de RF adequado, usando os seguintes componentes de gerenciamento de energia da Analog Devices:

- Comutador de RF ADRF5160

- Amplificador de baixo ruído (LNA) HMC8411

- Filtro passa-faixa sintonizável digitalmente ADMV8526

- Atenuador de passo digital (DSA) de RF HMC1119

- Amplificador controlador HMC8413

- PA HMC8205B

A Analog Devices oferece suporte abrangente ao desenvolvimento de software por meio de documentação e pacotes de software para baixar. Os desenvolvedores que utilizam o hardware de desenvolvimento mencionado acima podem prosseguir com a prototipagem e o desenvolvimento com base no software da linha de produtos da Analog Devices ou em pacotes de software de código aberto.

Este artigo limita a discussão a seguir ao software da linha de produtos. Para obter mais informações sobre a metodologia de desenvolvimento de código aberto, consulte o Guia do Usuário da Plataforma de Prototipagem ADRV9001/2 da Analog Devices.A Analog Devices estipula que o termo "ADRV9001" na documentação de suporte da empresa é entendido como um designador de família que abrange o ADRV9002 e outros membros da família ADRV9001. Consequentemente, as referências ao ADRV9001 no texto ou nas figuras abaixo se aplicam ao dispositivo ADRV9002 que é o foco deste artigo.

Disponível por meio da distribuição do kit de desenvolvimento de software (SDK) da linha de produtos da Analog Devices, a ferramenta Transceiver Evaluation Software (TES) baseada em Windows da empresa oferece um ponto de partida acessível para configurar e avaliar rapidamente o desempenho do transceptor.

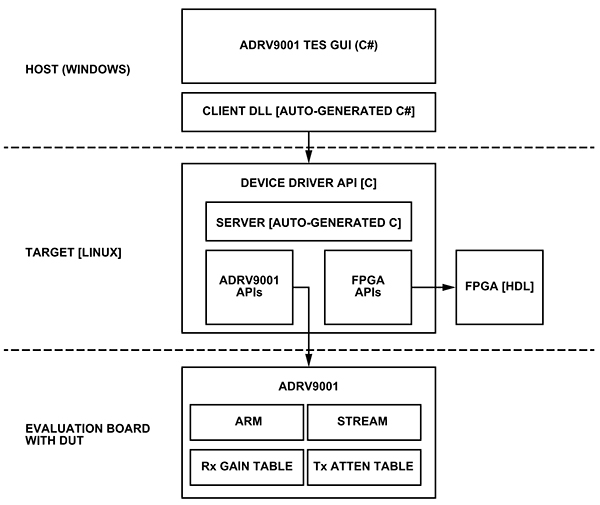

Durante a avaliação e a criação de protótipos com as placas baseadas no ADRV9002 da Analog Devices e a placa de teste ZCU102 da AMD, a ferramenta TES fornece uma interface gráfica do usuário (GUI) para configurar o hardware e observar os dados capturados (Figura 5).

Figura 5: A ferramenta TES do pacote SDK permite que os desenvolvedores comecem a avaliar rapidamente o transceptor ADRV9002 na plataforma de avaliação compatível. (Fonte da imagem: Analog Devices)

Figura 5: A ferramenta TES do pacote SDK permite que os desenvolvedores comecem a avaliar rapidamente o transceptor ADRV9002 na plataforma de avaliação compatível. (Fonte da imagem: Analog Devices)

Por sua vez, a ferramenta TES gera automaticamente o código C# que pode ser compilado no ambiente Linux, no ambiente MATLAB ou no Python. O SDK fornece um conjunto completo de bibliotecas de software e interfaces de programação de aplicativos (APIs), incluindo o pacote de APIs ADRV9001 desenvolvido para a plataforma AMD ZCU102.

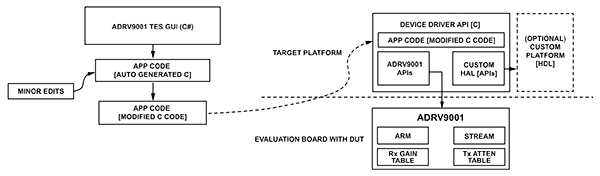

O fluxo do SDK também suporta diretamente a migração da avaliação e prototipagem com a placa de teste para o ambiente de destino personalizado do desenvolvedor (Figura 6).

Figura 6: A arquitetura do SDK permite que os desenvolvedores estendam facilmente os resultados de sua avaliação para sua própria plataforma de destino. (Fonte da imagem: Analog Devices)

Figura 6: A arquitetura do SDK permite que os desenvolvedores estendam facilmente os resultados de sua avaliação para sua própria plataforma de destino. (Fonte da imagem: Analog Devices)

Nesse fluxo de migração, o desenvolvedor permite que o TES gere o código automaticamente como antes. No entanto, em vez de usá-lo diretamente, o desenvolvedor implanta uma versão editada do código gerado na plataforma de destino. Na prática, as edições necessárias se limitam principalmente à remoção de chamadas de função que fazem referência a componentes de hardware reconhecidos pela ferramenta TES, mas que não são necessários no sistema de destino. A arquitetura do SDK inclui uma interface de camada de abstração de hardware (HAL) entre a biblioteca ADRV9001 e o hardware dos desenvolvedores, de modo que os desenvolvedores só precisam fornecer código personalizado que implemente o código da interface HAL para seu hardware específico. Como resultado, os desenvolvedores podem passar rapidamente da avaliação usando as placas da Analog Devices e a placa AMD para o desenvolvimento de seu ambiente personalizado de destino.

Conclusão

As aplicações ADEF enfrentam desafios crescentes em um ambiente de sinais cada vez mais complexo. Além de atender à demanda por maior desempenho em uma faixa mais ampla de frequências, os desenvolvedores precisam reduzir o SWaP para dar suporte à migração dessas aplicações para sistemas alimentados por bateria. Usando um transceptor altamente integrado da Analog Devices, os desenvolvedores podem implementar soluções SDR para atender a esses requisitos de forma mais eficaz.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.