Entenda e minimize o impacto do jitter em links de alta velocidade

Contributed By DigiKey's North American Editors

2023-12-21

Os osciladores de clock fornecem o batimento cardíaco de temporização dos circuitos modernos, estimulando os componentes do sistema. À medida que as velocidades do sistema aumentam para centenas de megahertz (MHz) ou mais, esses clocks precisam ser mais rápidos e oferecer jitter muito baixo, normalmente abaixo de 100 femtossegundos (fs), para manter o desempenho do sistema. Eles também devem manter suas especificações de baixo jitter ao longo do tempo, apesar das variações de temperatura e tensão.

Alguns jitters são induzidos por ruído e distorção do caminho do sinal e podem ser reduzidos de alguma forma com o uso de técnicas de repetição do clock e da temporização. No entanto, o jitter também é gerado pela fonte de clock, que geralmente é um oscilador. Isso se deve a vários fenômenos físicos, incluindo ruído térmico, imperfeições do processo, ruído da fonte de alimentação, outros ruídos externos que entram no oscilador de clock, tensões mecânicas no material e muitos outros fatores sutis. Independentemente da fonte, cabe ao projetista fazer todo o possível para minimizar o jitter inerente de clock, pois as deficiências não são reversíveis.

Este artigo discute os problemas de jitter a partir de várias perspectivas. Em seguida, ele apresenta os diferentes osciladores de clock da Abracon LLC e mostra como o jitter pode ser minimizado, combinando o desempenho do oscilador de clock com a aplicação.

Noções básicas de jitter

O jitter do clock é o desvio de uma borda do clock em relação à sua posição ideal no tempo. Esse jitter afeta a precisão e a exatidão da transmissão dos sinais de dados que o sinal de clock está estimulando, levando à degradação da relação sinal/ruído (SNR) no circuito de decodificação/demodulação do receptor ou em outros CIs do sistema. Isso resulta em uma taxa de erro de bit (BER) mais alta, aumento das retransmissões e redução da taxa de transferência de dados efetiva.

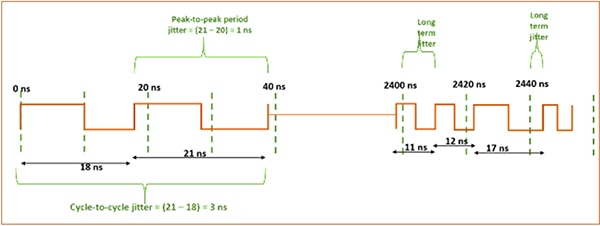

Devido à sua importância crítica, o jitter do clock é amplamente analisado em sistemas que passam um sinal de uma fonte de transmissão para um receptor por meio de cabos, conectores ou placas de circuito. Dependendo da aplicação, ele pode ser caracterizado de várias maneiras, incluindo jitter de ciclo a ciclo, período e de longo prazo (Figura 1).

Figura 1: O termo "jitter" abrange muitas variações de temporização, incluindo jitter de ciclo a ciclo, jitter de período e jitter de longo prazo. (Fonte da imagem: VLSI Universe)

Figura 1: O termo "jitter" abrange muitas variações de temporização, incluindo jitter de ciclo a ciclo, jitter de período e jitter de longo prazo. (Fonte da imagem: VLSI Universe)

- O jitter de ciclo a ciclo significa a alteração no período do clock em dois ciclos consecutivos e não está relacionada à variação da frequência ao longo do tempo.

- O jitter de período é o desvio de qualquer período de clock em relação ao seu período médio. É a diferença entre os períodos de clock ideal e real, e pode ser especificado como jitter de período de raiz quadrada média (RMS) ou jitter de período de pico a pico.

- O jitter de longo prazo é o desvio da borda do clock de sua posição ideal em um período de tempo mais longo. É algo análogo à deriva.

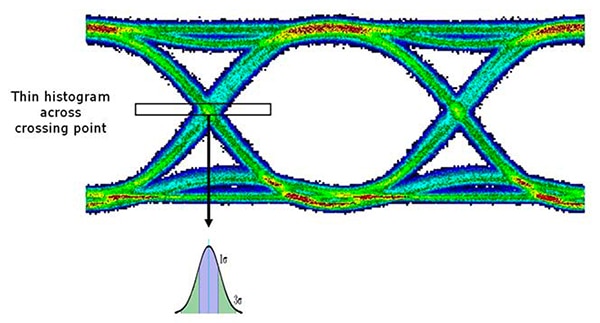

O jitter pode corromper a temporização usada por outras subfunções, componentes ou sistemas utilizados para obter uma recuperação de dados de baixa BER ou componentes em ritmo, como elementos de memória ou processadores em um sistema síncrono. Isso é visto no diagrama ocular da Figura 2 como uma ampliação do ponto de cruzamento na temporização do bit.

Figura 2: Em um diagrama ocular, o jitter é visto como uma ampliação do ponto crítico de cruzamento da temporização no fluxo de dados. (Fonte da imagem: Kevin K. Gifford/Univ. do Colorado)

Figura 2: Em um diagrama ocular, o jitter é visto como uma ampliação do ponto crítico de cruzamento da temporização no fluxo de dados. (Fonte da imagem: Kevin K. Gifford/Univ. do Colorado)

Para links de dados seriais, o circuito na extremidade receptora deve tentar restabelecer seu próprio clock para otimizar a decodificação do fluxo de dados. Para isso, ele deve sincronizar e bloquear o clock de origem, geralmente usando uma malha de captura de fase (PLL). O jitter afeta a capacidade do sistema de fazer isso com precisão, comprometendo sua capacidade de recuperar os dados com uma baixa BER.

Observe que o jitter pode ser medido nos domínios do tempo e da frequência; ambos são perspectivas igualmente válidas do mesmo fenômeno. O ruído de fase é uma visão no domínio da frequência do espectro de ruído em torno do sinal do oscilador, enquanto o jitter é uma medida no domínio do tempo da precisão da temporização do período do oscilador.

As medições de jitter podem ser expressas de várias maneiras. É comumente citado usando unidades de tempo, como "jitter de 10 picossegundos" (ps). O jitter de fase de raiz quadrada média (RMS) é um parâmetro no domínio do tempo derivado da medição do ruído de fase (domínio da frequência). Às vezes, o jitter também é chamado de jitter de fase, o que pode ser confuso, mas ainda é o parâmetro de jitter no domínio do tempo.

À medida que as frequências de operação do link e seus clocks aumentam de algumas dezenas de MHz para centenas de MHz ou mais, o jitter permitido na fonte de clock diminui para cerca de 100 fs ou menos. Essas frequências se aplicam a módulos ópticos, computação em nuvem, redes e Ethernet de alta velocidade, funções e aplicações que exigem uma frequência portadora entre 100 e 212/215 MHz e taxas de dados de até 400 gigabits por segundo (Gbps).

Gerenciando o cristal

A maneira mais comum de criar um sinal de clock estável, consistente e de frequência precisa é usar um oscilador de cristal de quartzo. Um circuito oscilador associado suporta o cristal. Há muitas famílias de circuitos desse tipo, cada uma com várias vantagens e desvantagens. Os cristais têm sido usados nessa função desde a década de 1930 para comunicação de rádio sem fio nas bandas de RF de média frequência (300 quilohertz (kHz) a 3 MHz) e alta frequência (3 a 30 MHz).

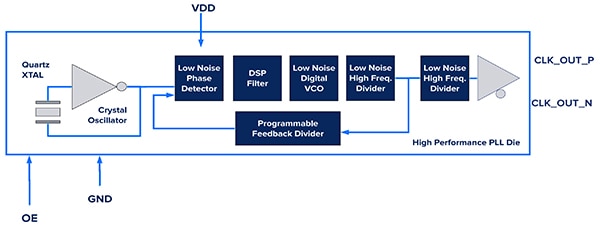

Uma abordagem amplamente utilizada para gerar clocks de jitter baixo é usar uma das muitas variações de arquiteturas baseadas em PLL. Por exemplo, os dispositivos das famílias AX5 e AX7 ClearClock™ da Abracon são fornecidos em invólucros de 5 × 3,2 milímetros (mm) e 5 × 7 mm, respectivamente, e usam uma tecnologia PLL sofisticada para um desempenho superior de jitter baixo (Figura 3).

Figura 3: Os osciladores de clock Abracon AX5 e AX7 usam um dos muitos projetos baseados em PLL, mas com aprimoramentos sutis para minimizar o jitter. (Fonte da imagem: Abracon)

Figura 3: Os osciladores de clock Abracon AX5 e AX7 usam um dos muitos projetos baseados em PLL, mas com aprimoramentos sutis para minimizar o jitter. (Fonte da imagem: Abracon)

Juntamente com a frequência de operação e o projeto do oscilador, o desempenho do jitter é afetado pelo tamanho físico do cristal de quartzo no núcleo do oscilador. À medida que o tamanho desse cristal é reduzido, torna-se mais desafiador oferecer um desempenho superior de jitter RMS.

Para soluções de clock na faixa de 100 a 200 MHz e em fatores de forma menores do que os dispositivos AX5 e AX7 baseados em PLL, é necessária uma nova arquitetura de oscilador. Esses requisitos de tamanhos menores estão normalmente associados aos transceptores e módulos ópticos de última geração. Há quatro maneiras estabelecidas de projetar um oscilador de clock na faixa de 100 a 200 MHz:

- Use um oscilador de quartzo com um bloco de quartzo de mesa invertido como elemento ressonador

- Use um oscilador de quartzo com um bloco de quartzo de terceiro sobretom como elemento ressonador

- Use uma malha do oscilador baseada em um bloco de quartzo de modo fundamental/terceiro sobretom abaixo de 50 MHz ou um oscilador de cristal com compensação de temperatura abaixo de 50 MHz, acoplada a um CI PLL de modo inteiro ou fracionário

- Use uma malha do oscilador baseada em ressonador de sistemas microeletromecânicos (MEMS) abaixo de 50 MHz acoplada a um CI PLL de modo inteiro ou fracionário

A opção 1 não oferece o melhor desempenho de jitter RMS, nem é a solução mais econômica. A opção 3 é complicada e tem deficiências de desempenho, enquanto a abordagem do ressonador MEMS da opção 4 não atende aos principais critérios de desempenho de 200 fs de jitter RMS máximo. Por outro lado, a opção 2 usa um bloco de quartzo de terceiro sobretom projetado de forma otimizada, levando em consideração a geometria dos eletrodos e a otimização do ângulo de corte. Essa combinação é ideal em termos de custo, desempenho e tamanho.

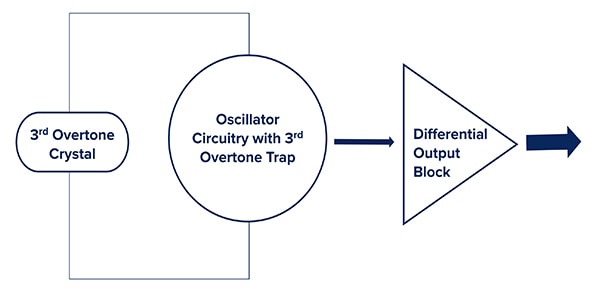

Usando essa abordagem, a Abracon desenvolveu soluções ClearClock de "terceiro sobretom" (Figura 4). Esses dispositivos usam uma arquitetura mais silenciosa para permitir um desempenho superior de jitter RMS ultrabaixo e extrema eficiência energética em invólucros miniaturizados, tão pequenos quanto 2,5 × 2,0 x 1,0 mm.

Figura 4: A solução ClearClock de "terceiro sobretom" da Abracon usa uma arquitetura mais silenciosa para melhorar o desempenho geral e a eficiência energética. (Fonte da imagem: Abracon)

Figura 4: A solução ClearClock de "terceiro sobretom" da Abracon usa uma arquitetura mais silenciosa para melhorar o desempenho geral e a eficiência energética. (Fonte da imagem: Abracon)

Nesse esquema, o projeto cuidadoso do bloco de cristal de terceiro sobretom, juntamente com a filtragem e o "aprisionamento" adequados do sinal da portadora desejada, garante um excelente desempenho de jitter RMS nas frequências desejadas de portadora.

Essa arquitetura não usa uma abordagem PLL típica, portanto, não há conversão ascendente. Consequentemente, não há necessidade de multiplicação fracionária ou inteira de PLL padrão, e a frequência de saída final tem uma correlação de um para um com a frequência ressonante do cristal de quartzo de terceiro sobretom. A ausência de multiplicação fracionária ou inteira simplifica o projeto e permite um jitter mínimo no menor tamanho possível.

Especificações e desempenho na prática

Os osciladores de clock são mais do que apenas um cristal e seu circuito analógico. Eles incluem circuitos de buffer para garantir que a carga de saída do oscilador e suas variações de curto e longo prazo não afetem o desempenho da unidade. Eles também suportam vários níveis de saída lógica digital diferencial para compatibilidade de circuitos. Essa compatibilidade elimina a necessidade de um CI externo de conversão de nível lógico. Esse CI aumentaria o custo, a pegada e o jitter.

Como os osciladores de clock são usados em muitas aplicações diversas com diferentes tensões, eles devem ser oferecidos em uma variedade de tensões de alimentação, como +1,8 volts, +2,5 volts ou +3,3 volts, bem como valores personalizados que normalmente variam de 2,25 a 3,63 volts. Eles também devem estar disponíveis com diferentes opções de formato de saída, como lógica positiva de baixa tensão/com pseudo-acoplamento de emissor (LVPECL) e sinalização diferencial de baixa tensão (LVDS), além de outros formatos.

Uma olhada em duas famílias de osciladores de clock a cristal, o AK2A e o AK3A, demonstra o que pode ser realizado por meio de uma compreensão e integração sofisticadas de materiais, projeto, arquitetura e teste. As duas famílias são semelhantes, sendo que as diferenças mais marcantes são o tamanho e a frequência máxima.

A família AK2A: Essa família de osciladores a cristal é oferecida em frequências nominais de 100 a 200 MHz e está disponível com tensões operacionais de 2,5 volts, 3,3 volts e 2,25 a 3,63 volts com lógica de saída diferencial LVPECL, LVDS e HCSL.

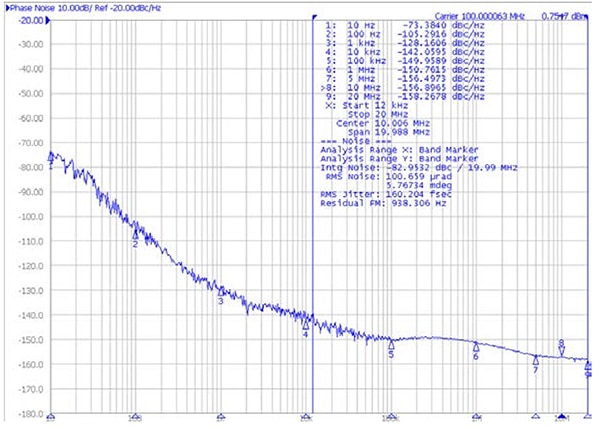

Todos os membros da família têm desempenho semelhante, incluindo baixo jitter RMS. Por exemplo, o AK2ADDF1-100.000T é um dispositivo de 100,00 MHz e 3,3 volts com saídas LVDS e um jitter RMS de 160,2 fs (Figura 5). Sua estabilidade de frequência é excelente, com mais de ±15 partes por milhão (ppm) em relação à temperatura, e é fornecido em um invólucro de dispositivo para montagem em superfície (SMD) de seis condutores, medindo 2,5 × 2,0 × 1,0 mm.

Figura 5: O jitter é mostrado como sendo de 160 fs para o AK2ADDF1-100.000T, um dispositivo de 3,3 volts e 100 MHz com saídas LVDS. (Fonte da imagem: Abracon)

Figura 5: O jitter é mostrado como sendo de 160 fs para o AK2ADDF1-100.000T, um dispositivo de 3,3 volts e 100 MHz com saídas LVDS. (Fonte da imagem: Abracon)

No entanto, à medida que as frequências de clock aumentam, o jitter deve diminuir para manter o desempenho ao nível de sistema. Para o AK2ADDF1-156.2500T, um oscilador LVDS de 156,25 MHz, o jitter RMS típico cai para 83 fs.

A família AK3A: Os dispositivos da família AK3A são um pouco maiores do que os da família AK2A, com uma pegada de 3,2 × 2,5 × 1,0 mm (Figura 6). As versões estão disponíveis e especificadas para 212,5 MHz, um pouco acima do limite de 200 MHz da família AK2A.

Figura 6: Os osciladores de cristal AK3A (à direita) são ligeiramente mais longos e mais largos do que os da série AK2A (à esquerda); há versões disponíveis para frequências de até 212,5 MHz, em comparação com 200 MHz do AK2A. (Fonte da imagem: Abracon)

Figura 6: Os osciladores de cristal AK3A (à direita) são ligeiramente mais longos e mais largos do que os da série AK2A (à esquerda); há versões disponíveis para frequências de até 212,5 MHz, em comparação com 200 MHz do AK2A. (Fonte da imagem: Abracon)

As especificações gerais desse dispositivo AK3A são semelhantes às do membro correspondente da família AK2A. Um exemplo é o AK3ADDF1-156.2500T3, um oscilador LVDS de 156,25 MHz que tem um jitter RMS típico de 81 fs, um pouco melhor do que o membro correspondente da família AK2A.

O jitter de ambas as famílias varia de acordo com a frequência de operação, a tensão de operação, o tamanho do invólucro e a escolha das saídas.

Considerações adicionais na prática

Não é suficiente ter um oscilador de clock que funcione de acordo com as especificações apenas no dia em que sai da fábrica. Como acontece com todos os componentes, especialmente os analógicos e passivos, esses osciladores estão sujeitos a derivas ao longo do tempo devido ao envelhecimento dos materiais constituintes e às tensões mecânicas internas.

Essa realidade é especialmente desafiadora para os osciladores de clock de alto desempenho, pois não há maneiras convenientes ou simples de corrigir, ou compensar essa deriva adicionando software, ou circuitos inteligentes. No entanto, há algumas maneiras de atenuar os efeitos da deriva. Isso inclui longos períodos de burn-in pelo usuário final para acelerar o envelhecimento do oscilador ou o uso de um oscilador com temperatura estabilizada em um gabinete controlado por forno. O primeiro consome muito tempo e é um desafio para a cadeia de suprimentos, enquanto o segundo é grande, caro e consome muita energia.

Reconhecendo que o envelhecimento é um parâmetro crítico, a família ClearClock da Abracon oferece uma precisão de frequência rigorosa e abrangente durante toda a vida útil do produto final de 10 a 20 anos. A Abracon garante a conformidade com a estabilidade de frequência de mais de ±50 ppm durante esse período. Isso é obtido por meio da seleção e da fabricação cuidadosas do cristal de terceiro sobretom e do seu condicionamento para atender à estabilidade de ±15 ppm entre -20°C e +70°C e à estabilidade de ±25 ppm entre -40°C e +85°C.

Como sempre, a engenharia trata-se de vantagens e desvantagens. As séries Abracon AK2A e AK3A oferecem melhor desempenho de jitter-ruído em comparação com suas séries anteriores (ger. I AK2 e AX3, respectivamente), usando um oscilador ASIC da próxima geração (ger. II), garantindo assim um desempenho de jitter RMS ultrabaixo.

Essa melhoria é obtida ao custo de um pequeno aumento no consumo de energia. O consumo máximo de corrente aumenta de 50 miliamperes (mA) da Geração I para 60 mA da Geração II, embora os dispositivos de baixa tensão funcionem com cerca de metade desse valor. Os osciladores ClearClock de segunda geração, portanto, fornecem jitter RMS ultrabaixo e ainda mantêm um baixo consumo de energia.

Conclusão

Os osciladores de temporização são o batimento cardíaco de um link de dados ou função de clock, e sua precisão, jitter e estabilidade são parâmetros essenciais para atingir o desempenho necessário ao nível de sistema, incluindo SNR alto e BER baixo. Frequências de clock mais altas podem ser obtidas com seleções de materiais e arquiteturas inovadoras que atendem às rigorosas especificações de desempenho exigidas pelo setor e seus diversos padrões. As séries Abracon AK2A e AK3A apresentam jitter abaixo de 100 fs na faixa de 100 a 200 MHz em invólucros SMD, medindo apenas alguns milímetros de cada lado.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.